# MIKROIŞLEMCI KONTROLLU ÇOK KAVŞAKLI TRAFIK SISTEMI Halil KARAKAŞ

Yuksek Lisans Tezi Elektrik Elektronik Mühendisliği Anabilim Dalı

1992

Anadolu Universites

## MIKROIŞLEMCI KONTROLLU ÇOK KAVŞAKLI TRAFIK SISTEMI

Halil KARAKAŞ

Anadolu Universitesi

Fen Bilimleri Enstitusu Lisansustu Yönetmeliği Uyarınca

Elektrik - Elektronik Muhendisliği Anabilim Dalı

Elektronik Bilim Dalında

YUKSEK LISANS TEZI

Olarak Hazırlanmıştır.

Danışman: Doç. Dr. Hamdi ATMACA

Halil KARAKAŞ'ın 'Yuksek Lisans' tezi olarak hazırladığı 'MIKROIŞLEMCI KONTROLLU ÇOK KAVŞAKLI TRAFIK SISTEMI' başlıklı bu çalışma, jürimizce lisansüstü yönetmeliğinin ilgili maddeleri uyarınca değerlendirilerek kabul edilmiştir.

Uye: Prof. Dr. Atila BARKANA

Uye: Doc. Dr. Hamdi ATMACA

Uye: Y. Doc. Dr. Osman PARLAKTUNA

Fen Bilimleri Enstitüsü Yönetim Kurulu'nun 27 MAYIS 1992 gün ve .314..5.. sayılı kararıyla onaylanmıştır.

Prof. Dr. Rustem KAYA Enstitu Muduru

## ICINDEKILER

|     |         |                                                | payia |

|-----|---------|------------------------------------------------|-------|

| UZ: | ET      |                                                | iv    |

| SU  | MMARY   |                                                | v     |

| TE  | ŞEKKU:  | R                                              | ٧i    |

| ŞEI | K f LLE | R DIZINI                                       | vii   |

|     |         |                                                |       |

| 1.  | GIRI    | \$                                             | 1     |

| _   |         |                                                |       |

| 2.  |         | ALIZASYON PROJELERININ TEMEL ILKELERI          | 4     |

|     |         | Sinyal Devresi                                 | 4     |

|     | 2.2.    | Faz Düzenleri                                  | 5     |

|     |         | 2.2.1. Sinyalize yaya geçitleri                | 5     |

|     |         | 2.2.2. Tek yönlü yolların kesiştiği kavşaklar  | 6     |

|     |         | 2.2.3. Sola dönüşlerin az olduğu kavşaklar     | 6     |

|     |         | 2.2.4. Uç ve dört fazlı uygulamalar            | 7     |

|     |         | 2.2.5. Ada çevresinde dönüş                    | 11    |

|     | 2.3.    | Yeşillerarası Süreler                          | 1 1   |

|     |         | 2.3.1. Sarı süreler                            | 11    |

|     |         | 2.3.2. Kırmızı ve Sarı süreler                 | 14    |

|     |         | 2.3.3. Koruma süreleri                         | 14    |

|     |         | 2.3.4. Kayıp zaman                             | 16    |

|     | 2.4.    | Yaya Geçiş Süreleri                            | 16    |

|     | 2.5.    | Devre Suresi                                   | 17    |

|     |         | 2.5.1. Etkili akım                             | 17    |

|     |         | 2.5.2. Devre suresi bileşkeleri                | 18    |

|     | 2.6.    | Optimum Devre Suresi                           | 19    |

|     |         |                                                |       |

| З.  | GENE    | L HABERLEŞME SISTEMLERI                        | 20    |

|     | 3.1.    | Dijital Haberleşmeye Giriş                     | 21    |

|     | 3.2.    | Paralel Data Transferi                         | 21    |

|     | 3.3.    | Seri Data Transferi                            | 22    |

| 4.  | וממחמ   | NIM                                            | 24    |

| ٠.  |         | Z-80 Mikroişlemci                              | 24    |

|     |         | Saat (Clock) Devresi                           | 26    |

|     |         | Reset Devresi                                  | 26    |

|     |         | Z-80 PlO (Paralel Giriş-Çıkış Birimi)          | 27    |

|     |         |                                                |       |

|     | 4.5.    | Hafıza Giriş-Çıkış Uniteleri İçin Adres Çözücü | 28    |

## IÇINDEKILER (devam)

|     |       |       |       |     |     |       |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   | Say | <u>/fa</u> |

|-----|-------|-------|-------|-----|-----|-------|-------|-----|-----|-----|-----|-----|-----|-----|----|-----|---|----|----|----|---|------|-----|-----|---|------|---|-----|------------|

|     |       | 4.5   | 5.1.  | Ha  | fì  | za    | l a   | rı  | n   | а   | rt  | e s | s 1 | er  | m  | es  | i |    | •  |    |   |      |     |     |   |      |   |     | 28         |

|     |       | 4.5   | 5.2.  | Gi  | r i | ş - ( | ; 1 l | kı: | ş   | üı  | n i | t∈  | e l | e r | i  | ni  | n | а  | d: | re | 5 | l e  | ומי | m e | 5 | i    |   |     | 28         |

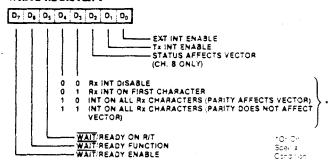

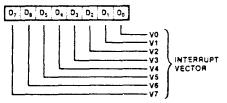

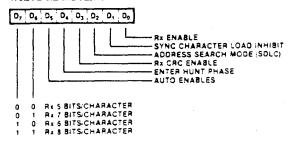

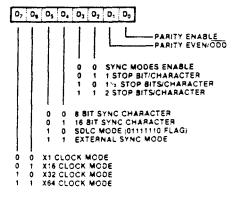

|     | 4.6.  | Z - 8 | 30 S  | 10  | (5  | er:   | i (   | Gi  | ri  | ş   | -Ç  | 1 } | (1  | ş   | В  | ir  | i | mi | )  | •  | • |      |     |     |   |      |   |     | 29         |

|     | 4.7.  | Z-8   | 80 C. | TC  | (5  | ау:   | 1 C   | ı,  |     | Za  | a m | ar  | ıI  | аy  | 11 | C 1 |   | Βi | r  | im | i | )    |     |     | • |      |   |     | 29         |

|     | 4.8.  | Gös   | ster  | ge  |     | • •   | • •   |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     | 30         |

|     | 4.9.  | Tuş   | Tal   | kım | 1   | • • • |       |     |     |     | •   |     | •   |     |    |     | • |    |    |    |   |      |     |     |   |      | • |     | 30         |

|     | 4.10. | . Ir  | ter   | rup | t   | Ara   | a I   | )e  | vr  | e 9 | 5 i |     |     |     | •  |     |   |    |    |    |   |      | •   |     | ٠ |      | • |     | 32         |

|     | 4.11. | . Si  | ste   | nin | Ç   | al:   | ŞI    | na  | S 1 | •   | •   |     | •   |     |    |     | • |    | •  | ٠. |   |      | •   |     | • |      | • |     | 33         |

| 5.  | YAZII | LIM   |       |     |     |       |       |     |     |     |     |     |     |     |    |     | • |    |    |    |   |      |     |     |   |      |   |     | 35         |

|     | 5.1.  | Akı   | ș D   | iya | gr  | am:   | aı    | 1   |     |     |     |     | •   |     |    |     |   |    | •  |    |   | • .• |     |     |   |      |   |     | 35         |

| 6.  | SONUÇ | CLAF  | 2     |     |     | • • • |       |     |     |     |     |     | •   |     |    |     |   |    | •  |    |   |      |     |     | • | •, • |   |     | 46         |

| 7.  | KAYNA | AKLA  | R D   | ZI  | Nİ  |       |       | • • |     |     |     |     | •   |     | •  |     | • |    |    |    |   | •    | •   |     |   |      | • |     | 47         |

| EKL | ER    |       |       |     |     |       |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     |            |

| 1.  | Z-80  | Mik   | rois  | şle | mc  | i     |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     |            |

| 2.  | Z-80  | PIC   | )     |     |     |       |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     |            |

| з.  | Z-80  | CTC   | ;     |     |     |       |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     |            |

| 4.  | Z-80  | SIC   | )     |     |     |       |       |     |     |     |     |     |     |     |    |     |   |    |    |    |   |      |     |     |   |      |   |     |            |

5. Sistem Programları

#### UZET

Bu tez çalışmasında belirlenen yol kavşaklarındaki trafik ışıklarının bir merkezden kontrolü esas alınmış ve tasarlamıştır. Her bir kavşakta bulunan mikroişlemciler ile merkezi mikroişlemci arasında yıldız - çevre bağlantısı (star - loop connection) kurulmuş ve seri bir haberleşme hattı oluşturulmuştur. Merkezi mikroişlemciden her kavşakta mikroişlemciye veya her bir kavşaktaki mikroişlemciden merkezi mikroişlemciye bilgi transferi yapmak mümkün olmuştur. Merkezi kontrol sistemiyle kavşaklardaki trafik ışıklarının devre süreleri günün trafik yoğun luğuna göre hesaplanacak ve her kavsaktaki mikroişlemciye seri veri (data) hattından gönderilecektir. şekilde yapılan düzenleme ile trafik akısındaki gecikmeler ve zaman kaybı ortadan káldırılacaktır.

#### SUMMARY

In this thesis, the control of the traffic lights in road confluents from a central microprocessor is aimed, and is planned. Star - loop connection is constructed between central microprocessor and microprocessors that exist each confluent, therefore a serial communication link established between them. It is possible to make data transfer from central microprocessor to microprocessors that exist in each confluent or from microprocessors that in each confluent to central microprocessor. The period of the traffic lights in confluents will bе calculated according to the traffic density of the day, and will be sent from serial data link to microprocessors that exist in each confluent. In this case, delays in traffic flow and time loss will be avoided in rush hours.

### **TEŞEKKUR**

Çalışmalarımda her aşamada bana yardımcı olan ve beni yönlendiren değerli hocam Doç. Dr. Hamdi ATMACA 'ya, Yard. Doç. Dr. Osman PARLAKTUNA 'ya ve mesai arkadaşlarım Arş. Gör. Hakan TORA ,Arş. Gör. Salih EREN ve Arş. Gör Umit KUNKÇU 'ye ve benden manevi desteğini esirgemeyen sevgili arkadaşım Selda DURAN 'a teşekkür ederim.

## ŞEKILLLER DIZINI

| <u>Şeki</u> | <u>1</u>                                           | Sayfa |

|-------------|----------------------------------------------------|-------|

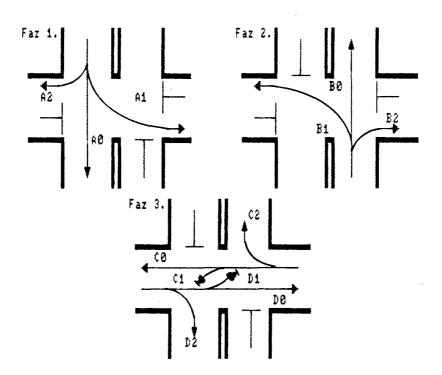

| 2.1.        | Yaya Geçidi Fazları                                | . 5   |

| 2.2.        | Tek Yönlü Yol Kavşaklarında Fazlar                 | . 6   |

| 2.3.        | Sola Donuşun Az Olduğu Kavşakta Fazlar             | . 7   |

| 2.4.        | Sola Dönüşleri Ayrılan 3 Fazlı Düzen               | . 8   |

| 2.5.        | Sola Dönüşleri Birlikte 3 Fazlı Düzen              | . 9   |

| 2.6.        | T - Kavşaklarda Faz Düzenleri                      | . 10  |

| 2.7.        | Ada Çevresinde Dönüş                               | . 11  |

| 2.8.        | Kritik Kavşak Ölçüleri                             | . 12  |

| 3.1.        | Haberleşmenin Topolojik Yapıları                   | . 21  |

| 3.2.        | Yıldız - Çevre (Star-Loop Connection) Bağlantısı . | . 21  |

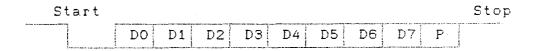

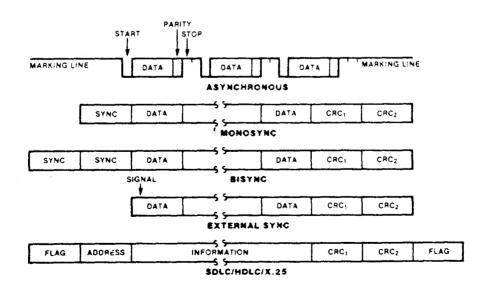

| з.з.        | Asenkron Data Haberleşme Formatı                   | . 22  |

| 3.4.        | BISYNC Haberleşme Formatı                          | . 23  |

| 4.1.        | Mikroişlemci Kartı                                 | . 25  |

| 4.2.        | Saat (Clock) Devresi                               | . 26  |

| 4.3.        | Resetleme Devresi                                  | . 26  |

| 4.4.        | PIO Baglantisi                                     | . 27  |

| 4.5.        | PIO 1le Trafik İşiklarının Bəğlantısı              | . 27  |

| 4.6.        | Adres Çözücü Devresi                               | . 28  |

| 4.7.        | SIO - TSC232 Bağlantıları                          | . 29  |

| 4.8.        | CTC Bağlantısı                                     | . 30  |

| 4.9.        | Gösterge Bağlantısı                                | . 31  |

| 4.10.       | . Tuş Takımı                                       | . 31  |

| 4.11.       | . Interrupt Ara Devresi                            | . 32  |

| 4.12.       | . MUX - DEMUX Devresi                              | . 32  |

| 5.1.        | Kavşaktaki İşık Kontrolü İçin Akış Şeması          | . 37  |

| 5.2.        | Sinyalize Bir Tesisin Çalışmasının Akış Şeması     | . 38  |

| 5.3.        | Sistem Programı Akış Şeması                        | 39    |

| 5.4.        | Merkez Mikroislemci Sistem Programı Akıs Seması .  | . 42  |

### 1.GIRIŞ

Sinyaller, bir diğer deyişle ışıklı işaretler, yollar üzerinde ve özellikle kavşaklarda düzenli ve güvenli bir akım sağlamak için kullanılan trafik kontrol gereçleridir.

ilk olarak 1868 yılında Londra' da el ile yönetilen semaforlar biçiminde kullanılan trafik sinyalleri gece görünümlerini sağlamak amacı ile gaz lambaları ile aydınlatılmıştır. Kırmızı ve yeşil ışıklı ilk sinyalizasyon tesisi 1914 yılında A.B.D.'nde Cleveland'da kurulmuş, 1920 yılında Detroit'te sarı ışıklar da kullanılmıştır. 1924 yılından sonra Avrupa ülkelerinde de kullanılmaya başlanan ışıklı sinyaller özellikle 1950 yılından sonra büyük gelişme göstermiştir (1).

Herhangi bir yerde sinyalizasyon tesisi kurulması için aşağıdaki maddelerden en az birinin gerçekleştirilmesi gerekmektedir:

- a) Kesişen akımlardan veya geometrik özelliklerden dolayı oluşan gecikmeleri, sıkışmaları ve tıkanıklıkları önlemek.

- b) Taşıtların diğer taşıtlarla veya yaya geçitleri ile kesiştikleri noktalarda güvenli bir geçiş düzeni sağlamak ve kaza ihtimalini azaltmak,

- c) Taşıt ve yaya yoğunluklarını göz önünde tutarak, akım yönlerine geçiş hakkı veya önceliği verirken uyumlu bir zaman dağıtımını yapmak,

- d) Yüklü trafik yoğunluğu olan bir yol üzerindeki taşıtları zaman zaman durdurarak tali yollardaki trafiğe ve yayalara da geçiş olanağı sağlamak.

Trafik güvenliği ve kontrolü için kullanılan yatay ve düşey işaretlemelerde (Yol çizgilerinde ve trafik levhalarında) olduğu gibi, ışıklı işaretlerin de aşağıdaki dört niteliğe sahip olmaları gereklidir.

- 1. Surucu ve yayaların dikkatini çekmelidir.

- 2. Basit ve kesin anlamları olmalıdır.

- 3. Sürücü ve yayaların saygı göstermeleri ve uymaları sağlanmalıdır.

- 4. Üzellikle sürücülere intikal ve reaksiyon için yeterli zaman tanınmalıdır.

Trafik sinyalizasyonu sistemlerinin gerek projelendirilmesi gerekse uygulaması oldukça basit görünmekle birlikte küçümsenmemeli, kullanılacak cihaz ve gereçler ihtiyaca uygun biçimde titizlikle seçilmeli ve ne yetersiz nede fazla olmalıdır. Zaman dağıtımlarında taşıt ve güvenliğine titizlik gösterilmeli, değişik yonlerine verilen geçiş hakki süreleri yönlerin yoğunluklarının birbirlerine olan oranları ve sinyalize edilmiş tesisten geçiş süreleri ile uyumlu olmalıdır. Zaman dağıtımlarında özellikle akım değerlerinin saatlik, günlük, aylık, mevsimlik değişimleri göz önünde tutulmalı, ayrıca zaman aşımı nedeniyle akım özelliklerinin değişmesi halinde sürekli bir revizyon yapılmalıdır. Gereksiz olarak kurulmuş elemanları, yanlış yerleştirilmiş veya uyumsuz işletilen bir sinyalizasyon tesisi gecikmeleri büyük ölçüde arttırabilir ve bunun sonucu olarak sürücü ve yayaları ışıklara uymamaya alıştırabilir, hatta zorlayabilir (1,2).

Bu projede belli başlı kavşaklar göz önüne alınmış ve bu kavşaklardaki trafik akışını kontrol edebilecek bir sistem hazırlanmıştır. Bu sistemde dört ayrı kavşak bir merkezden bilgisayar aracılığı ile kontrol edilmektedir. Merkez bilgisayar ile her kavşakta bulunan yardımcı bilgisayarlar arasında bilgi alış verişini sağlamak için bir haberleşme hattı kurulmuştur. 3. Bölümde haberleşme ile ilgili açıklamalar yapılacaktır.

Kullanılan bu sistemde kavşakların kontrolu için gereken bilgiler günün belirli saatlerinde merkez bilgisayar aracılığı ile her kavşaktaki yardımcı bilgisayar'a gönderilecek ve sistemin düzgün bir şekilde çalışması sağlanacaktır. Kavşaklardaki taşıtların bekleme ve geçiş

süreleri günün değişen saatlerinde (Trafik yoğunluğuna göre) merkez bilgisayar tarafından kayıp zamanı en aza indirecek şekilde kontrol edilir.

#### 2. SINYALIZASYON PROJELERININ TEMEL ILKELERI

#### 2.1. Sinyal Devresi

Sinyalize bir tesiste birbirini izleyen değişik ışıklı sinyallerin bir devrine "Sinyal Devresi" veya kısaca "Devre" denir. Işıklı sinyallerin bir devreyi tamamlaması sırasında geçen toplam zamana da "devre süresi" veya "period" adı verilir.

Bir devre süresi iki bileşenden oluşur:

- 1. Taşıt akımları için ayrılan yeşil sürelerin toplamı

- 2. Yeşiller arasındaki sürelerin toplamı (kayıp zaman)

Bir sinyalize tesisin verimi buyuk ölçüde devre süresinin uyumlu seçilmiş olup olmadığına bağlıdır. Bu nedenle devre süresinin saptanması sinyalizasyon projesinin hemen hemen en önemli bölümüdür. Pratikte uygulanabilecek minimum yeşil sürelerinin altına düşülmediği sürece, taşıt ve yayalara verilecek yeşil süreler devre süresinin uzunluğuna bağlıdır. Yeşiller arasında kalan süreler ise kabul edilen kıstaslara göre saptanır veya hesaplanır. Yeşiller arasında kalan sürelerin fazla olması bir devre içinde kayıp zamanı arttırır ve devre süresinin uzamasına yol açar.

Pratikte 30 sn'den daha kısa devre süresinin yeterli olacağı bir kavşak için "sinyalizasyon tesisinin kurulmasını gerektirmeyen bir kavşak" denebilir. Yayalara geçiş hakkı verecek olan yeşil süre 6 sn'den daha kısa olmamalıdır. 8 sn'den daha kısa olan taşıt yeşil süreleri ise pratikte uygulanabilme olanağı bulamamaktadır. Sinyalizasyon sistemlerinde 120 sn'den daha uzun devre süreleri uzun kuyrukların oluşmasına yol açar. Zorunlu şartlar altında 135-140 sn'lik devre süreleri maksimum olarak kabul edilebilir. Devre süresine bağlı olarak saptanan yeşil süreler için herhangi bir üst limit yoktur.(3)

### 2.2. Faz Düzenleri

Bir sinyal devresi içinde belirli bir trafik akımını, veya birden fazla akımı aynı anda öngören kumanda şekline "faz" adı verilir. Sinyalizasyon Projesinde seçilecek faz sistemi kavşağa giriş olan yol sayısına ve kesişen trafik yoğunluğuna bağlıdır.

Sinyalize bir tesiste en az 2 ve en çok 4 fazlı sistemler uygulanır. Taşıt trafiği ile birlikte yaya trafiğinin çok yoğun olduğu bazı kavşaklarda, sinyalize yaya geçitlerinde olduğu gibi özel yaya fazları düzenlenebilir. Faz sayısının çok olması, her faz arasındaki yeşiller arası süreyi arttıracağından yeşiller arası sürelerin toplamı olan kayıp zamanın fazla olması ise devre süresinin uzamasını gerektireceğinden, proje hazırlanırken faz sayısının mümkün olduğu kadar azaltılmasına çalışılmalıdır.

### 2.2.1. Sinyalize yaya geçitleri

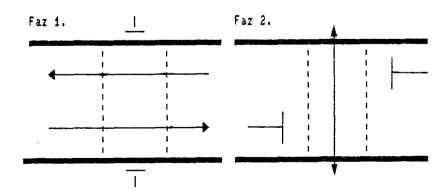

Kavşak olmayan yerlerdeki yaya geçitlerinin sinyalize edilmesinde bir taşıt, birde yayalar için olmak üzere iki faz kullanılır (Şekil 2.1).

Şekil 2.1 Yaya Geçidi Fazları

### 2.2.2. Tek yönlü yolların kesiştiği kavşaklar

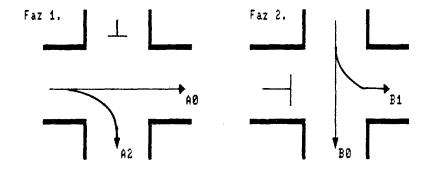

Tek yönlü yolların birleştiği üçlü kavşaklarda kavşağa doğru bir taşıt akımı olup, ana yola katılan trafik sola dönüş yapıyorsa sola dönüşün yoğun olması halinde sinyalizasyon gerekebilir. Bunun dışında bir kavşaktaki yönlerin tümü tek yönlü ise, sinyalizasyon tesisi kurulması için en az bir kesişme noktası öngörülür.

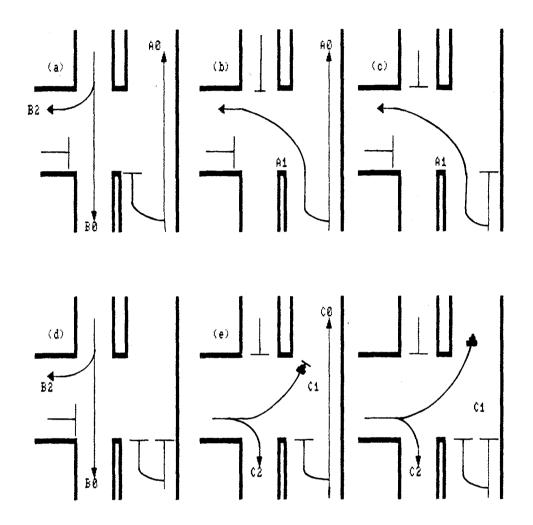

Dört beş kollu kavşaklarda Şekil 2.2 'de görüldüğü gibi bir fazlı bir düzen yeterlidir. Şekildeki örnekte  $B_1$  sola dönüşü ile  $A_2$  sağa dönüşünü yapan taşıtlar trafik kuralları uyarınca, aynı anda geçiş hakkı olan yayalara yol vereceklerdir.

Şekil 2.2. Tek Yönlü Yol Kavşaklarında Fazlar

#### 2.2.3. Sola dönüşlerin az olduğu kavşaklar

Çift yönde akımı bulunan yollarda sola dönüş yapan taşıt hacmi 60 taşıt/saat veya daha az ise, bunların sola dönüşleri için özel bir donanım yapmak gerekmez. Sola dönüş yapacak taşıtların keseceği trafik akımının arasında boşluk olmasa bile az sayıda taşıt fazların değişimi sırasındaki yeşiller arası süreden yararlanarak dönüş manevrasını rahatlıkla yapabilir. Ayrıca, dönüş yapacak taşıtların karşı yönünden kavşağa giren taşıtlar arasında zaman zaman boşluklar oluşuyorsa daha fazla sayıda taşıt bu boşluklardan yararlanarak sola dönüşünü tamamlayabilir. Kavşak alanının

geniş ve yeterli olması halinde, sola dönüş yapacak taşıtların kavşak içinde depo edilerek, yeşiller arası sürenin uzatılması suretiyle ek bir fazın uygulanmaması sağlanabilir.

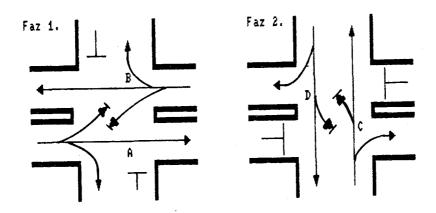

Şekil 2.3 'te çift yönlü yolların kesiştiği dörtlü bir kavşakta sola dönüşlerin az olmasından yararlanılarak uygulanan iki fazlı bir düzen görülmektedir. Bu şekilde faz düzenine göre sağa dönüşler düz gidişler ile birlikte kesilmektedir. Kavşağın geometrik özellikleri uygun olursa sağa dönüşler bütün fazlarda serbest bırakılabilir, ancak bu dürümda sağa dönüş yapacak taşıtların geçiş hakkı olan taşıtları sıkıştırmamasına ve sağa sapmadan önceki yaya geçidinin yayalara açık olmamasına dikkat edilmelidir. Aynı prensibler çok fazlı düzenlerde de söz konusudur.

Şekil 2.3 Sola Dönüşün Az Olduğu Kavşakta Fazlar

### 2.2.4. Üç ve dört fazlı uygulamalar

Duz gidiş yapan taşıt yoğunluğunun yanı sıra sola dönüş yapan taşıt sayısının artması halinde çok fazlı düzen uygulaması gerekmektedir. Çok fazlı sinyalize düzen kurulması tasarlanan kavşakların faz sayısının azaltılması olanakları araştırılmalı, bu amaçla tek bir çözüm ile yetinilmeyip değişik alternatifler denenmelidir. Çok fazlı uygulamanın giderilemiyeceği kavşaklarda hangi durumlarda nasıl bir düzenin uyumlu olacağı aşağıda belirtilmiştir:

- 1) Karşılıklı İki Sola Dönüşün Yoğun Olduğu Kavşaklar:

- a) Sola dönüşler için yeterli sığınma şeridi varsa şekil 2.4 te gösterilen üç fazlı düzenin uygulanması yerindedir. Bu düzende yoğun sola dönüşler için bir faz ayrılmaktadır.

Şekil 2.4. Sola Dönüşleri Ayrılan Uç Fazlı Düzen

- b) Sola dönüşler için yeterli sığınma şeridi yoksa şekil 2.5 teki üç fazlı düzen kullanılmaktadır. Bu düzende yoğun sola dönüş akımlarına düz gidiş akımları ile birlikte geçiş hakkı verilmektedir.

- 2) İkiden Fazla Sola Dönüşün Yoğun Olduğu Dörtlü Kavsaklar:

Bu kavşaklarda dört fazlı düzen uygulanmalıdır.

a) Sola dönüşler için yeterli sığınma şeridi bulunmayan kavşaklarda Şekil 2.5 deki 1. ve 2. fazlardan sonra C ve D yönlerine ayrı geçiş hakkı verilir. Bu biçimde tasarlanan dört fazlı uygulamalarda fazlar değişik sıralarda

düzenlenebilir, ancak kayıp zamanın minimum tutulması için birbirini izleyen fazların saatin akış yönünde olmamasına çalışılmalıdır. Bunun amacı, kavşağı boşaltmakta olan son taşıt ile kavşağa girecek ilk taşıtın arasındaki uzaklığın mümkün mertebe fazla olmasını sağlamaktır.

b) Sola dönüşler için yeterli sığınma şeritleri bulunan kavşaklarda yukarıda açıklanan dört fazlı düzen uygulanabildiği gibi Şekil 2.4 te gösterilen 1. ve 2. fazlardan sonra 3. fazda  $C_0$  ve  $D_0$  düz gidişlerine geçiş hakkı verilir, 4. fazda da  $C_1$  ve  $D_1$  sola dönüş akımları sığınma şeritlerini boşaltırlar.

Şekil 2.5. Sola Dönüşleri Birlikte Üç Fazlı Düzen

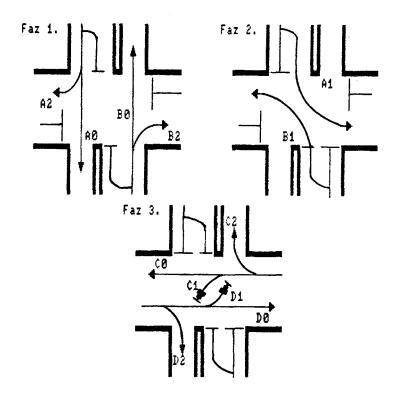

3) Sola dönüşlerin yoğun olduğu T-kavşaklar

Bu kavşaklarda genellikle 3 fazlı bir düzen uygulanır. Kavşak geometrisine ve taşıt yoğunluklarının birbirine oranına göre Şekil 2.6 daki fazlardan üçü seçilir.

Sekil 2.6. T - Kavşaklarda Faz Düzenleri

- a) Ana yolda yeterli sığınma şeridi vərsa 1. ve 2. faz olarak (a) ve (c) , sığınma şeridi yoksa (b) ve (d) kullanılır.

- b)  $A_0$  akımının  $B_0$  akımından çok fazla olduğu durumlarda (a) hareketinden sonra 2. faz olarak (c) hareketi kullanılır.

- c) 3. faz genellikle (f) hareketindeki gibi olmakla birlikte  $A_0$  akımının çok yoğun olması veya ana yolu kesen yaya trafiği bulunmayıp B yönüne doğru kavşaktan açılan yolun  $A_0$  ve  $C_1$  akımlarının birbirine katılmaları halinde her ikisini birden taşıyabilecek nitelikte olması durumunda (e) hareketi uygulanabilir.

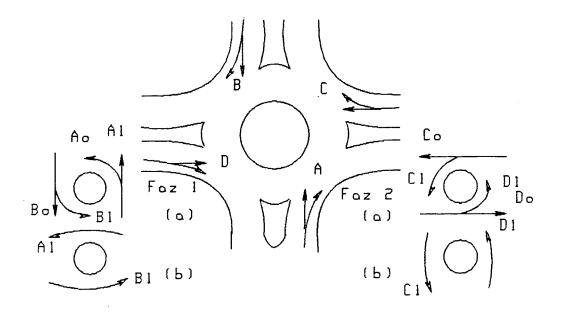

#### 2.2.5 Ada cevresinde donus

Şekil 2.7 de sinyalize edilmiş bir dönel kavşak görülmektedir. İki fazlı düzenle yönetilen bu kavşağın her iki fazının (a) hareketinde düz gidiş ile birlikte kavşağa giren sola dönecek taşıtlar ortadaki adanın çevresinde dönerek depolanmakta, (b) hareketinde ise kavşağı boşaltmaktadırlar. Sola dönüş yapacak taşıtlar kavşak içine girmiş olduklarından fazların (b) hareketleri için verilecek süre çok kısa olabilmekte, bir sonraki fazda kavşağa girecek taşıtlar kavşağı boşaltmakta olan taşıtlarla aynı yönde seyrettiklerinden zaman kaybı önlendiği gibi trafik güvenliği de büyük ölçüde arttırılmaktadır. Burada yayalara yeşil yanmadığı durumlarda sağa dönüşler serbest bırakılmıştır (3.4).

Şekil 2.7. Ada Çevresinde Dönüş

#### 2.3 Yeşiller Arası Süreler

### 2.3.1 Sarı süreler

Sarı ışıklı sinyalin amacı, taşıt sürücülerini geçiş hakkının sona ermiş olduğu hususunda uyararak, uzakta olanların duruşa geçmelerini ve duramayacak kadar yaklaşmış olanların kəvşağı güvenle geçerek boşaltmalarını

sağlamaktır. Bu nedenle, sinyalize bir tesiste devre süresi ve yeşil süreleri etkileyen en önemli faktörler taşıt yoğunluğu ve kompozisyonu olmasına rağmen, sarı süreler taşıtların sinyalize tesise yaklaşım hızlarına bağlıdır.

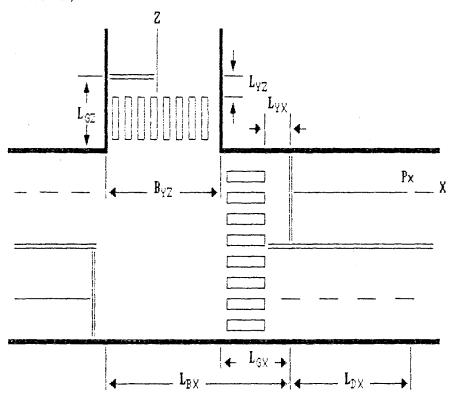

Şekil 2.8 de görülen basit T - tipi kavşakta, X yönüne geçiş hakkı verilirken kavşaktaki kritik ölçüler ve anlamları şunlardır:

- LDX = Duruş uzaklığı : X yönünden kavşağa yaklaşmakta olan taşıtın fren intikali ve reaksiyonu sırasında katettiği mesafe dahil olmak üzere güvenli duruş için kavşaktaki dur çizgisinden geride olması gereken uzaklık.

- $L_{\rm BX}$  = Boşaltma uzaklığı : X yönünden kavşağa giren bir taşıt için dur çizgisinden kavşaktaki kesişme noktalarının sonuna kadar olan uzaklık.

- $L_{GX}$  = Giriş uzaklığı : X yönünden sonra geçiş hakkı elde edecek Z yönü için dur çizgisinden kavşaktaki ilk kesişme noktasına kadar uzaklık.

Şekil 2.8. Kritik Kavşak Ölçüleri

Şekil 2.8 deki Fx noktası, X yönünden kavşağa giren tasıtlar için kritik bir noktadır. (Bu nokta aslında sabit olmayıp her taşıtın hızına göre değişik bir yerdedir, ancak proje hazırlanırken Fx noktası taşıtların %85 hızına göre yaklaşık olarak alınır). Yeşil ışıktan sonra sarı ışık yandığında Px noktasına erişmemiş olan taşıt teorik olarak  $L_{\rm DX}$  mesafesi içerisinde ve dur çizgisinden önce durabilecektir. Sarı ışık yandığı anda Px noktasını gecmiş olan bir taşıt ise dur çizgisine kadar duramayacağından, kırmızı ışık yanmadan kavşaktaki kesişme noktalarının bulunduğu alan içine girmiş olmalı, dolayısiyle ( $L_{\rm DX}$  +  $L_{\rm GX}$ ) mesafesini katedebilmelidir. X yönünden kavşağa girmekte olan taşıtların %85 hızı Vx km/saat ise, gerekli sarı ışık süresi Yx şu şekilde bulunur.

$$Y_X = \frac{3.6}{V_X} (L_{DX} + L_{g_X})$$

(2.1)

Asfalt kaplaması olan bir yolda ıslak zemin ile lastikler arasındaki sürtünme katsayısı yaklaşık olarak 0.35 dir. Intikal ve reaksiyon süresi ise ortalama olarak 1.0 saniye kabul edilebilir. Bu şartlar için yaklaşım yolunun meyilsiz olduğu kabul edilerek gerekli sarı ışık süreleri Tablo 1. de gösterilmiştir.

Genellikle sarı ışık süreleri minimum 3 saniye olarak alınır. Fratik uygulamalarda yaklaşık olarak 70 km/saat %85 hız için 4 saniye, 90 km/st için 5 saniye sarı ışık süresi uyumlu kabul edilebilir.

Tablo 1. Sarı ışık Süreleri (Y)

| %85                                    | hız                 |                         | Giriş uz                | aklığı(m)              |                            |

|----------------------------------------|---------------------|-------------------------|-------------------------|------------------------|----------------------------|

| km/st                                  | 0                   | 5                       | 10                      | 15                     | 20                         |

| 20<br>30<br>40<br>50<br>67<br>80<br>10 | 12233344.0<br>144.0 | 780371582<br>223334445. | 645703704<br>3333944455 | 500136926<br>444444455 | 465569148<br><br>544444555 |

#### 2.3.2 Kırmızı ve Sarı süreler

Herhangi bir yöne yeşil ışıkla geçiş izni verilmezden önce, harekete geçecek olan taşıtların hazırlanmaları ve zaman kaybetmemeleri için kırmızı ve sarı üniteler birlikte sinyal verirler. Bu ışıklı sinyal için metodik bir hesap uygulanmayarak duruma göre 2-3 saniyelik bir süre seçilir. Kırmızı ve Sarı ışıklı sinyalde taşıtların geçmemeleri ve beklemeleri gereklidir. Ancak yerel şartlara göre taşıt sürücüleri bu ışıklı sinyalde geçme eğilimi gösteriyorlarsa kırmızı ve sarı sürenin iki saniyeden uzun olmaması gerekir.

#### 2.3.3 Koruma süreleri

Koruma süresi, geçiş hakkı sona eren bir yönden kavşağa girerek kavşağı boşaltan son taşıt ile, bundan sonraki fazda kavşağa girecek ölan ilk taşıtın kesişme noktasında çarpışmamaları için fazlar arasında bırakılması gereken, ve yeşiller arası sürenin bir bölümünü oluşturan, kayıp bir zamandır. Güvenli bir koruma süresi hesaplamak için aşağıdaki kabulleri yapmak gerekir:

- a) Kavşağı boşaltmakta olan taşıt daha önce kırmızı ışıkta beklemiş olan kuyruğun son elemanıdır ve kavşağı önündeki taşıtların arkasında ağır bir hızla terketmektedir.

- b) Kavşağı terkedecek olan son taşıt sarı ışıklı sinyalde geçmektedir ve dur çizgisini geçtiği anda kırmızı ışıklı sinyal yanmaktadır.

- c) Bir sonraki fazda kavşağa girmek üzere dur çizgisinde bekleyen taşıt yoktur. Kavşağa ilk girecek olan taşıt hızını düşürmeden yaklaşmakta olup (kırmızı ve sarı) sinyalden sonra yeşil ışığın yandığı anda dur çizgisini geçmektedir.

Şekil 2.8 de X yönünden gelen akım, Z yönünden gelen akım tarafından izleniyorsa standart bir otomobil boyu 5m. olarak alındığı taktirde, kavşağı terketmekte olan son taşıtın bir sonraki fazdaki ilk taşıt kendisine yetişmeden

katetmesi gerekli olan mesafe  $(L_{BX}+5)$ m. dir. Z yönünden kavşağa girecek olan taşıtın ise, yeşil ışık yandığı andan sonra kesişme noktasına kadar katedeceği mesafe  $L_{GZ}$  dir. Her iki taşıt arasındaki koruma süresi aşağıdaki şekilde hesaplanır:

Boşaltma süresi :

$$t_{BX} = \frac{L_{BX} + 5}{V_{B}} \tag{2.2}$$

Burada

V<sub>B</sub> = Kavşağı boşaltmakta olan son taşıtın kavşak içindeki ortalama hızı (km/st),

$L_{\mbox{\footnotesize{BX}}}$  = X yönünden kavşağa giren taşıtın kavşağı boşaltma mesafesi,

Giriş süresi ise

$$t_{GZ} = 3.6 \frac{L_{GZ}}{V_Z}$$

(2.3)

Burada

$V_{\rm Z}$  = Geçiş hakkı açılacak olan yaklaşım yönünün %85 hızı,

$L_{GZ}$  = Geçiş hakkı açılacak olan yaklaşım yönünün giriş uzaklığıdır.

Kesişme noktasındaki çarpışmayı önlemek için kullanılacak koruma süresi ise iki sürenin farkı olacaktır:

$$t_K = t_B - t_G \tag{2.4}$$

Burada

t<sub>K</sub> = Koruma sūresi,

t<sub>B</sub> = Boşaltma süresi,

t<sub>G</sub> = Giriş süresidir.

Koruma süresinin hesaplanmasında en büyük zorluk  $V_{\rm B}$  ve  $V_{\rm Z}$  değerlerinin saptanmasıdır. Şehir içi kavşaklarının sinyalizasyon projelerinde %85 hız 50 km/saat şehir dışı yolları üzerindeki sinyalize kavşaklarda ise 80 km/saat olarak kabul edilmekle birlikte, gerçeğe yakın bir uygulama

yapılabilmesi için mevcut geometrik durum ve trafik şartları altındaki yaklaşık değerler gözlem yapılarak bulunmalıdır. Kavsakta beklemiş olan taşıtların kavşak içindeki ortalama hızları ise 25 km/st. mertebesinde kabul edilebilir.

#### 2.3.4. Kayıp zaman

Kayıp zaman, bir devre içindeki bütün yeşiller arası sürelerin toplamıdır. Başka bir deyişle, bir devre içindeki sarı süreler ile koruma sürelerinin ve koruma sürelerinin dışında kalan hep - kırmızı sürelerin toplamıdır.

$$t_{s} = \sum_{i=1}^{n} Y_{i} + \sum_{i=1}^{n} t_{ki} + \sum_{i=1}^{n} t_{R}$$

(2.5)

Burada

ts = Kayıp zaman.

tki=i fazı ile bir önceki faz arasındaki koruma süresi.

n = Faz sayısı.

Yi = i fazındaki akış yönü için verilen sarı süre.

ΣtR= Hep - kırmızı sürelerin toplamı (koruma süreleri hariç) dır.

#### 2.4. Yaya Geçiş Süreleri

Yaya trafiğinin yoğun olmadığı kavşaklarda, yaya gecis süreleri geçite dikey yöndeki taşıt trafiğinin kırmızı süre aralıklarında verilir. Yayalara geçiş hakkı verilmezden önce taşıtların kesinlikle durmuş olmaları gereklidir. Yayalara verilecek yeşil ışık süresinin 6 sn'den daha kısa olmamasına dikkat edilmelidir. Yayaların yeşil ışık süresi. yürüme hızı 1.2 m/sn kabul edilerek bulunur.

### Yaya Yeşili Süresi ≥ Yaya Geçidi Uzunluğu (By) /1.2 (2.6)

Yalnız yayalar için düzenlenmiş olan veya yaya trafiğinin yoğun olduğu geçitlerde ise her faz içinde karşıdan karşıya geçecek olan ortalama yaya sayısının göz önünde tutulması gerekir. Bunun için en uygun yontem ne kadar sayıda yayanın geçidi ne kadar zamanda geçtiğini gözlemek suretiyle bulmaktır. Gözlem yapılmayan geçitlerde ise aşağıdaki

kıstaslar yaklaşık olarak uygulanabilir:

- a) Yaya geçidinin her 1 m. genişliği için aynı anda karşılıklı birer yayanın geçebileceği düşünülmelidir.

- b) Geçiti, önundekinin arkasından geçmesi gereken her yaya için yaya geçiti 1 m. den daha uzunmuş gibi düşünülmüştür.

Orneğin 5 m. genişliğinde ve 10 m. uzunluğunda bir yaya geçidinde her faz içinde bir taraftan diğerine 15 yaya geçmesi gerekiyorsa, yayalar her sırada 5 kişi olmak üzere 3 sıra halinde geçeceğinden By = 12 m. olarak alınmalıdır. Dolayısıyla yayanın yeşil süresi en az 10 sn. koruma süresi de en çok 5 sn olmalıdır.

#### 2.5 Devre Süresi

Bir sinyalizasyon tesisinin pojesinde, geometrik özellikleri, seçilen faz düzenini ve trafik şartlarını göz önüne alarak saptanan Devre süresinin hesaplanması projenin hemen hemen en önemli bölümüdür.

Devre süresinin hesaplanması için değişik kıstaslar uygulayan çeşitli yöntemler geliştirilmiştir. Sinyalize edilecek olan alandaki gecikmelerin minimuma indirilmesini ve bu alanın kapasitesinin de göz önünde tutulmasını öngören rasyonel yöntemler de. bazı parametrelerin saptanmasında deneysel sonuçların ya da ampirik denklemlerin kullanılmasından kaçınamamaktadır. Bunun nedeni, taşıt özellikleri ile yaya ve sürücü davranışlarının kesin teorilere bağlanamamış olmasıdır.

#### 2.5.1 Etkili akım

Sinyalize bir tesisin herhangi bir fazında birden fazla yönde taşıt akımı aynı anda yer alabilir. Bir faz içindeki değişik taşıt akımlarından, otomobil birimi eşdeğeri olarak, şerit başına düşen yükü en yüksek olan, diğer bir deyimle otomobil birimi yükü en büyük olan yön o fazı kontrol eden yöndür.

Birbirini izleyen fazlardaki en yuksek yuku olan yonlerin hepsine birden Etkili akım yonleri, veya daha kısa olarak Etkili akım adı verilir. Birbirini izleyen fazlardaki en yüksek trafik yüklerinin toplamına da Etkili akım yükü denir. Örneğin iki fazlı bir sinyalizəsyon düzeni olan bir kavşağın her fazında iki ayrı yönde taşıt akımı varsa ve 1. fazdaki otomobil birimi yükleri Ma ve Mb , 2. fazdakiler de Mc ve Md ise, Ma ≥ Mb ve Mc ≥ Md olması halinde, etkili akım (Ma, Mc) ve etkili akım yükü de ∑M = Ma + Mc olacaktır.

#### 2.5.2 Devre süresi bileşkeleri

Herhangi bir devre süresi, kullanılan yöntem ve uygulanan sistem ne olursa olsun, prensip bakımından iki bileşkeden oluşur.

- a) Taşıt akımları için ayrılan yeşil süreler toplamı.

- b) Kayıp zaman.

Devre Suresi,

$$C = \sum_{i=1}^{n} G_{i} + t_{s}$$

(2.7)

ile ifade edilir. Burada

C : Devre suresi,

n: Faz sayısı,

G;: i fazını kontrol eden akımın yeşil ışık süresi,

ts: Kayıp zaman' dır.

Sinyalize yaya geçitlerinde, yayalar için verilen yeşil ışık süreleri taşıtlar için zaman kaybına yol açacağından, bu süreler hep-kırmızı süre kapsamına alınır ve dolayısıyla kayıp zaman olarak kabul edilir. Devre süresinin hesaplanmasında, kullanılan yöntemin özelliğine göre çeşitli faktörler göz önüne alınmakla birlikte, Etkili akım en önemli yeri tutar. Hemen hemen bütün yöntemlerde, etkili akım içindeki taşıtlara verilecek yeşil sürelerde devre süresinin ve aynı zamanda geçirecekleri akım yüklerinin fonksiyonu olurlar.

### 2.6 Optimum Devre Süresi

Uygulanan yöntem ne olursa olsun devre süresinin hesaplanmasında öncelikle ortalama akım değerleri kullanılır. Ortalama değerlere göre hesaplanan bir devre süresinin sakıncaları şu şekilde özetlenebilir:

- a) Kavşağa ortalamadan daha düşük sayıda taşıt geldiği zaman yeşil sürelerde kayıplar oluşacaktır.

- b) Kavşağa ortalamanın üstünde taşıt geldiği zaman kuyruklar uzayacak ve gecikmeler artacaktır.

Sinyalize edilen kavşağa ortalama değerlerden daha az taşıt geldiği zaman, kayıp yeşil süreler, ancak tesis uyarmalı olduğu taktirde önlenebilir. Kurulan tesis səbit zamanlı olursa devre süresinin kavşağa her yönden (veya isteğe göre yalnız bazı yönlerden) girecek olan taşıtların büyük bir oranının kendilerine verilecek yeşil süre içinde geçme imkanı elde etmesi, devre süresinin buna göre ayarlanması ile sağlanabilir. Bir diğer deyişle, etkili akımdaki bazı yönlerden veya hepsinden bir devre süresi içinde kavşağa giren taşıtların sayısı, ortalamanın üstünde olsa bile gelmekte olan taşıtların hepsini büyük bir ihtimalle (%90 - %95 gibi) geçirilmesi devre süresinin uzatılması ile gerçekleştirilebilir. Bu şekilde saptanan devre süresine Optimum Devre Süresi adı verilir (3,4).

#### 3. GENEL HABERLESME SISTEMLERI

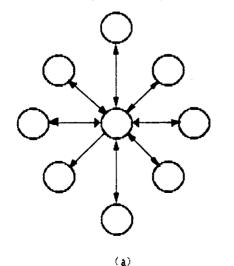

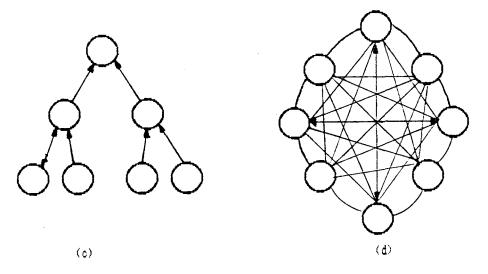

bölümde bilgisayarların birbirlerine değisik kombinasyonlarda bağlantı sekilleri üzerinde durulacaktır. Şekil 3.1 de dört değişik topolojik yapı görülmektedir. Sekil 3.1.a' da yıldız bağlantı (Star connection) görülmektedir. Burada yan ünitelerin çıkışları merkezdeki ana Uniteye bağlanmıştır. Bilgi akışı çift yönlüdür. Unitelerle merkez Unite arasında özel bir ayırıcı devre Sekil 3.1.b' de cevre bağlantı connection) görülmektedir. Bu bağlantı da Uniteler kendi aralarında bir çevre oluşturur. Her bir Unitenin çıkışı bir sonrakinin qirişine bağlanmıştır. Bu yapı tek olarak kullanıldığında merkezi ünite pozisyonu ortadan halkar. Unite gerektiğinde merkezi Unite kullanılabilir. Bilgi akışı tek yönlüdür. Sekil 3.1.c' de dallanma bağlantı (Tree connection) görülmektedir. Burada her bir Unite diğer bir Uniteye oradanda merkezi Uniteye bağlanmıştır. Bilgi akısı yan ünitelerden merkeze doğru tek yonludur. Şekil 3.1.d'de ise tam bağlantı (Completely connection) yapısı görülmektedir. Bu yapı, çok kalabalık Uniteleri temel alarak çalışır. İstenen Uniteden diğer Uniteye bilqi transferi yapılabilir ve bilqi akısı çift yonludur (5,6,7).

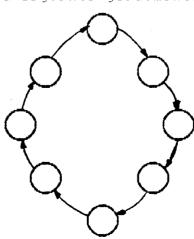

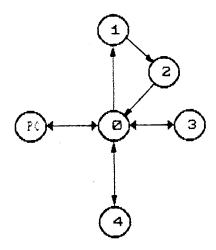

Gerçekleştirilen bu projede yıldız bağlantı (Star connection) ile çevre bağlantı (Loop connection) iç içe kullanılmıştır. Şekil 3.2 de bu bağlantı görülmektedir.

Şekil 3.1 Haberleşmenin Topolojik Yapıları

Şekil 3.2. Oluşturulan Çok Mikroişlemcili Sistem Yapısı

## 3.1 Digital Haberleşmeye Giriş

Seri ve paralel veri (data) transferi bilgisəyərlər arasında karşılıklı bilgi alış-veriş yöntemleridir. Her iki yöntemde geniş bir uygulama alanı bulmaktadır.

### 3.1.1 Paralel data transferi

Paralel veri (data) iletimi hızın önemli olduğu kısa mesafeli haberleşmelerde kullanılmaktadır. Bütün bir veri haberleşmesi çok hızlı bilgisayarlar arasında kurulmuştur ve bu haberleşmenin hızı saniyede milyon karaktere çıkabilmektedir.

#### 3.1.2 Seri veri transferi

Seri veri transferi genelde sayısal (digital) bilginin uzun mesafelere aktarılması gerektiği yerlerde kullanılır. Uzun mesafeli haberleşmede seri veri transferinin kullanılmasının tek sebebi bilgiyi taşımak için gerekli olan kablo sayısının az olmasından kaynaklanır. Fakat bu haberleşmede elde edilen transfer hızı bugünku normal telefon hatları kullanıldığında ancak 4800 bit/sn (baud rate) dir.

İki tür seri haberleşme metodu mevcuttur. Bunlar sırası ile asenkron haberleşme ve senkron haberleşmedir.

#### a) Asenkron veri transferi

Asenkron veri haberleşmesinin bir diğer adı da başla dur (start stop) haberleşmesidir. Çünkü senkronizasyonu sağlamak için gönderilen her 1 byte bilginin içinde başla ve dur bitleri bulunmaktadır. Asenkron haberleşmede clock (saat) sinyaline ihtiyaç yoktur. Çünkü senkronizasyon gönderilen başla ve dur biti ile sağlanır. Şekil 3.3 te asenkron haberleşmenin genel formatı verilmiştir. Gönderilecek her bilgiden önce lojik seviyesi 'low' olan bir sinyal gönderilir. Bunun ardından LSB ilk bilgi olacak şekilde veri gönderilir. Gönderilen verinin ardından istenirse veriye ait parite biti gönderilebilir. Stop biti her zaman veri bilgisinden sonra gelir ve lojik 'high' seviyesindedir (8).

Şekil 3.3 Asenkron Data Haberleşme Formatı

#### b) Senkron haberleşme

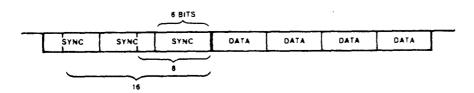

Senkron haberleşme de senkronizasyon bir veya iki senkronizasyon karakteri gönderilerek sağlanır ve ardından

uzun bir veri bloğu gönderilir. Senkronizasyon karakterinin haricinde birde clock pulsler gönderilir. Senkron haberleşme değişik şekillerde gerçekleşebilir. Burada örnek olarak BISYNCH (Binary Synchronous communication) yöntemini kısaca açıklamak yeterli olacaktır. Şekil 3.4 'te görüldüğü gibi veri gönderecek olan ünite diğer üniteye haberleşmenin başında her biri tek byte (8 bitlik bilgi) olan iki adet senkronizasyon karakteri gönderir ve karakterlerden hemen sonra transfer edilecek olan veri bloğunu gönderir. Veri gönderme işlemi sonunda ise gönderme işleminin sona erdiğini belirten bir karakter gönderir ve işlemi bitirir (8).

| Synchronizati | on   | Data | 3    |          |       |

|---------------|------|------|------|----------|-------|

| SYNCH SYNCH   | DATA | DATA | DATA | <br>DATA | END   |

| CHAR CHAR     | BYTE | BYTE | BYTE | BYTE     | OF    |

| 1 2           | 1    | 2    | 3    | N        | TRAN. |

Şekil 3.4 BISYNCH Haberleşme Formatı

#### 4. DONANIM

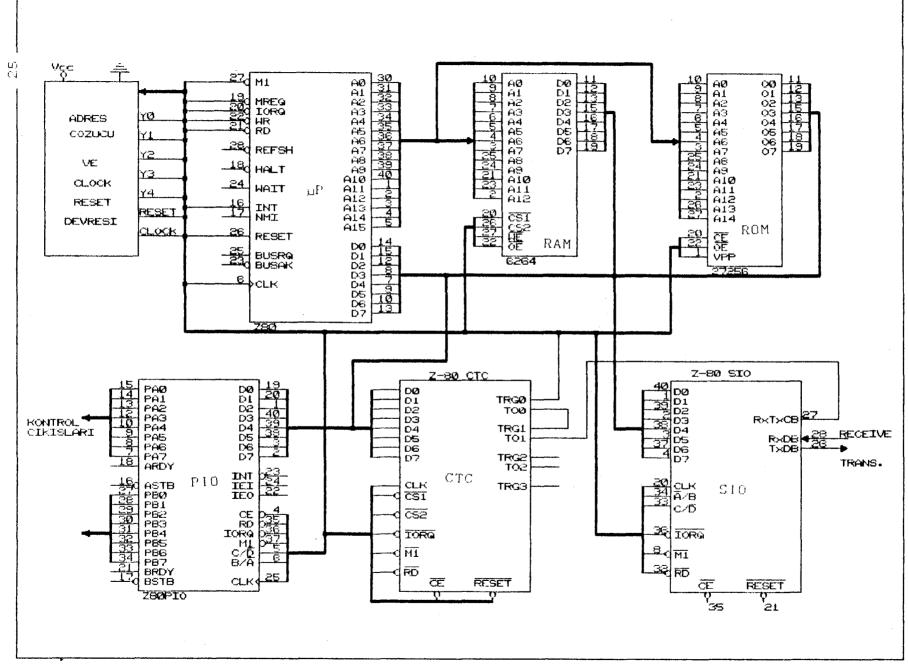

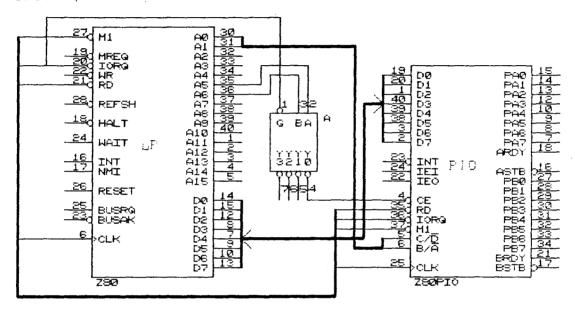

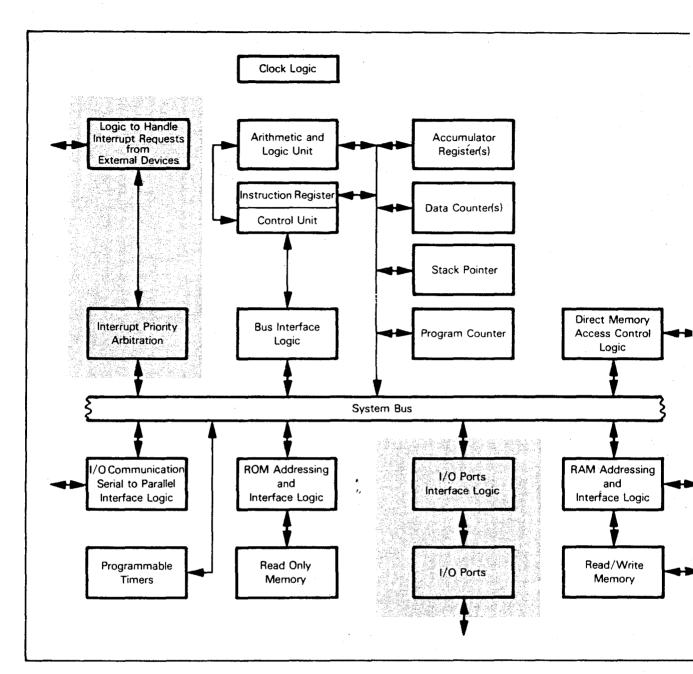

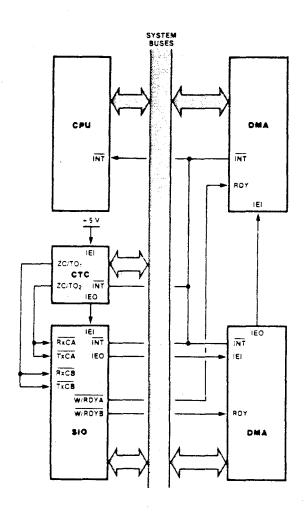

Bu projede kullanılan sistemin oluşturulması için 5 adet mikroişlemci kartı, 1 adet PC bilgisayar ve bu mikroişlemci kartlarının çok mikroişlemcili sistemi oluşturabilmeleri için bir ara devre hazırlanmıştır. Her mikroişlemci kartı üzerinde Z-80CPU, Z-80 PIO, Z-80 SIO, Z-80 CTC, 32Kbyte'lık ROM, 8Kbyte'lık RAM, gerekli adreslemeleri yapan adres çözücü devresi, saat sinyali devresi ve resetleme devresi mevcuttur. Ayrıca merkezi üniteyi PC bilgisayardan bağımsız olarak kullanabilmek için merkezi ünite için tüş ve gösterge devreleri ilave edilmiştir. Şekil 4.1 de bu mikroişlemci kartının bağlantısı görülmektedir.

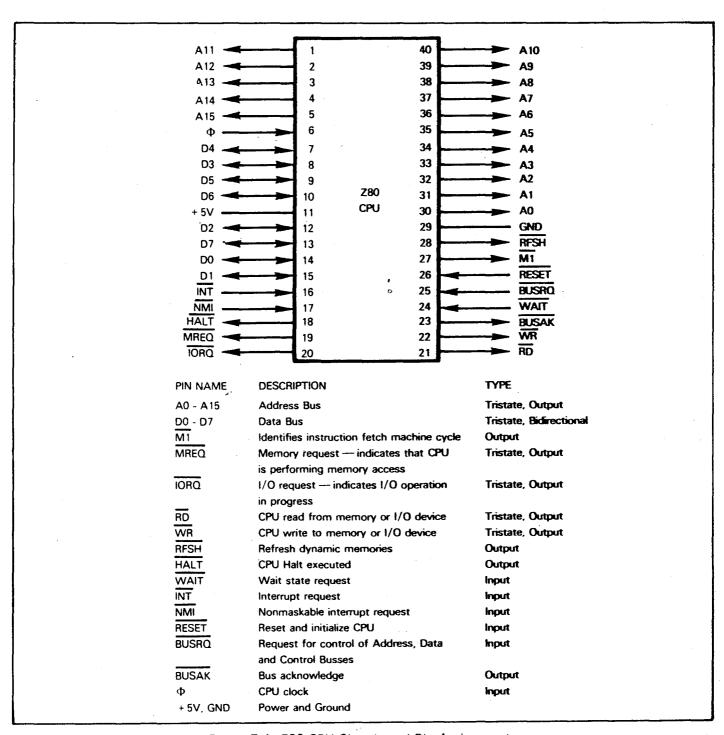

#### 4.1 Z-80 Mikroislemcisi

Z-80 mikroişlemcisi Z-80, Z-80A, Z-80B, Z-80H olarak sırasıyla 2, 4, 6. 8 MHz 'lik mikroişlemciler olarak Uretilir. Bu mikroişlemci, her ünitenin tüm işlevlerini yöneten, hafızalar ve giriş-çıkış uyum devreleri arasındaki bilgi işleme ve transfer işlemlerini gerçekleştiren birimdir. Z-80 CPU 8 bitlik mikroişlemciler içerisinde en populer olanıdır. Z-80 NMOS teknolojisinin belirli bir şeklini kullanır ve bu sebepten dolayı da bir adet +5 V'luk kaynak ile çalışabilir. Bunun diğerlerinden farklı olan özellikleri ise bir tane saat sinyalinin oluşu, dinamik hafıza refresh lojiği ve interrupt modlarının fazla olmasıdır.

Donanım açısından da büyük üstünlüklere sahiptir. Mikroişlemci genel amaclı yazaçlara (register), akümülatöre ve aritmetik mantık (ALU) ünitesine sahiptir. Diğer mikroişlemcilere kıyasla genel amaçlı yazaç sayısı daha fazladır. Komut sayısının ve yazaç sayısının fazlalığı programcıya büyük kolaylıklar sağlar. Hafıza ve giriş-çıkış (1/0) birimlerinin kontrolü için adres, bilgi ve kontrol giriş-çıkışlarına sahiptir.

Kart

emci

U'h krois

Ξ. ---

4

Sekil

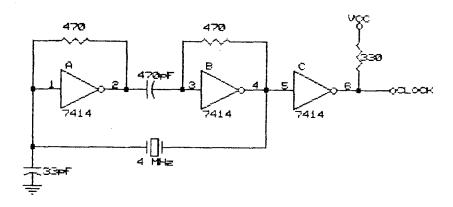

#### 4.2 Saat (Clock) Devresi

Z-80 mikroişlemci komutlarını fetch ve execute edebilmesi için çerekli kare dalgayı üreten kristallı osilator devresidir. Saat devresi çıkışı sistemde saat sinyaline ihtiyaç duyulan diğer çevre birimlerine de bağlıdır. Saat devresi şekil 4.2 de verilmiştir.

Şekil 4.2 Saat (CLOCK) Devresi

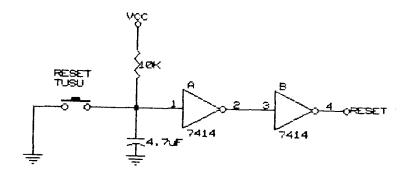

### 4.3 Reset Devresi

Bu devre Z-80 mikroişlemcisini ve bağlı olduğu diğer çevre elemanlarını resetlemek için kullanılır. Mikroişlemcinin resetlenmesinde program sayıcısına (program counter) 0000H bilgisi yüklenir ve büylece programın başlangıcına dönülür. Resetleme devresi şekil 4.3 de gösterilmiştir.

Sekil 4.3 Resetleme Devresi

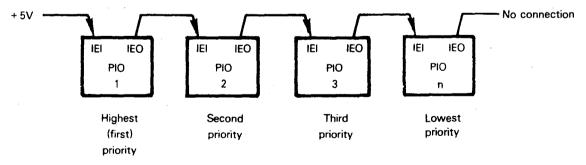

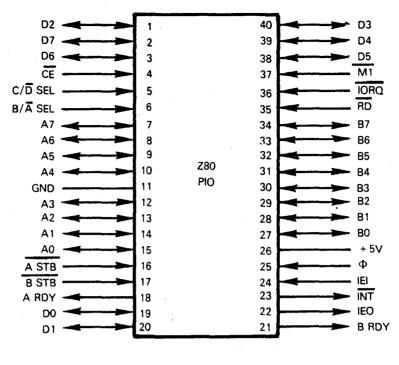

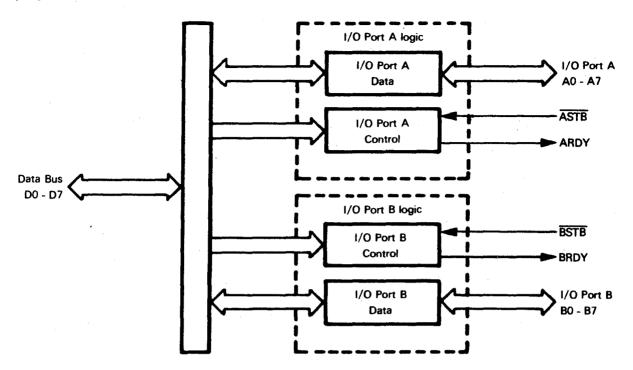

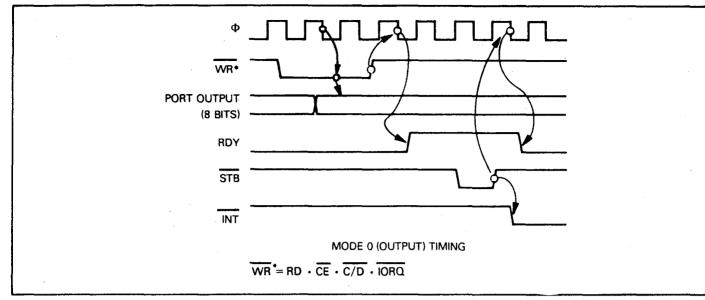

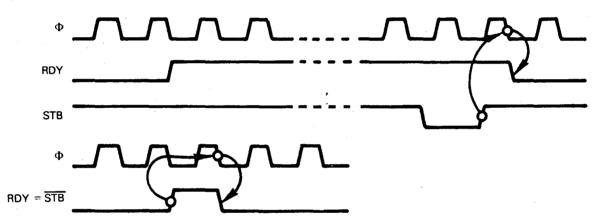

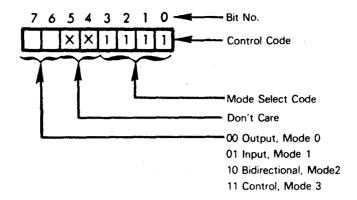

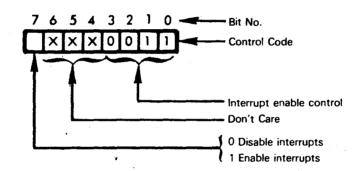

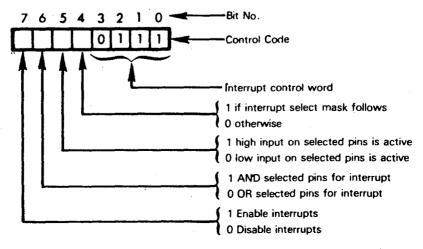

## 4.4 Z-80 PIO (Paralel Giriş-Çıkış Birimi)

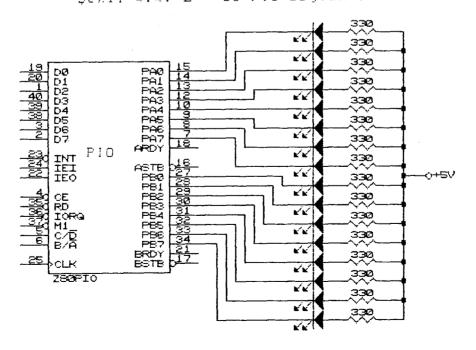

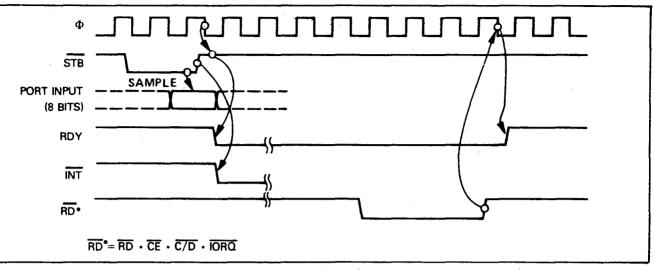

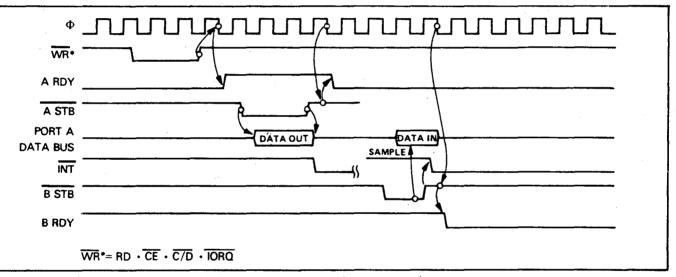

Giriş-çıkış Unitesi mikroişlemcinin dış dünya ile bilgi alış verişini sağlayan birimdir. PlO'nun Z-80 mikroişlemcisi ile bağlantısı şekil 4.4 te gösterilmiştir. Trafik ışıkları kontrolü için yapılan bağlantı şekil 4.5 te verilmiştir.

Sekil 4.4. Z - 80 PIO Bağlantısı

Şekil 4.5 PlO İle İşıkların Bağlantısı

# 4.5 Hafıza ve Giriş - Çıkış Üniteleri için Adres Çözücü

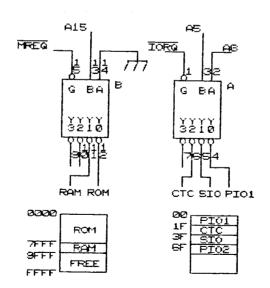

Sistemde 74LS139 adres kod çözücü tümleşik devresi kullanılmıştır. Bu entegrede iki adet 2x4 adres kod çözücü mevcuttur. Bunlardan bir tanesi hafıza üniteleri diğeri ise giriş-çıkış üniteleri için kullanılmaktadır.

#### 4.5.1 Hafızaların adreslenmesi

Hafizalardan hangisinin kullanılacağının belirlenmesi için A15 adres hattı kullanılmıştır. A15 low ise EPROM, high ise RAM aktif olmaktadır. MEMREQ sinyali kod cözücünün E girişine bağlanarak kod çözücünün yalnızca hafıza islemlerini yapması sağlanmıştır. Şekil 4.6.a da hafıza adres çözücü bağlantısı gösterilmiştir.

#### 4.5.2 Giriş/Çıkış ünitelerinin adreslenmesi

Çevre elemanlarının hangisinin kullanılacağını belirlemek için A5 ve A6 adres hatları kullanılmıştır. IORQ sinyali kod çözücünün E girişine bağlanarak sadece giriş/çıkış islemleri sırasında aktif olması sağlanmıştır. Şekil 4.6.b de giriş/çıkış adres çözücü devresi verilmiştir.

Sekil 4.6 Adres Cozucu; (a) Hafiza, (b) Giriş/Çıkış

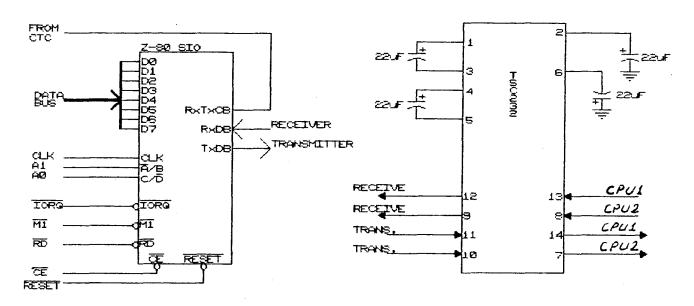

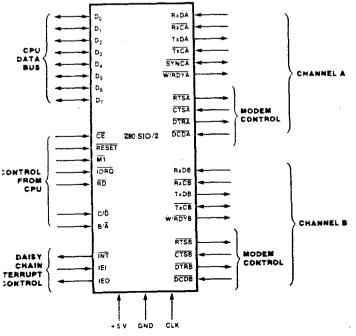

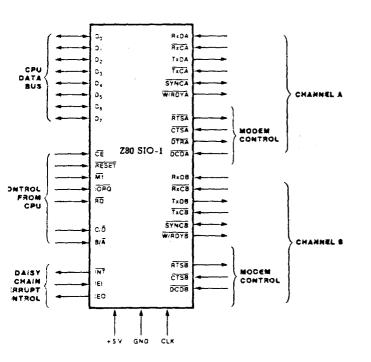

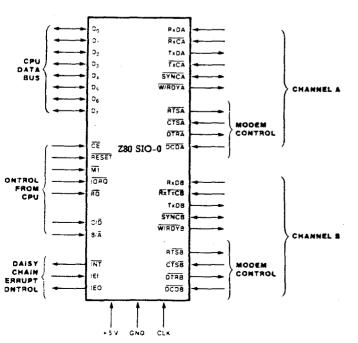

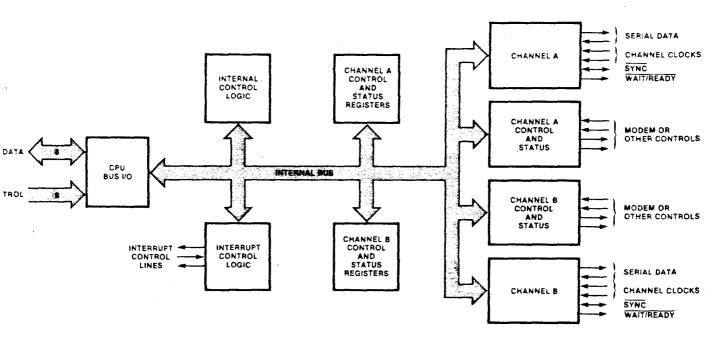

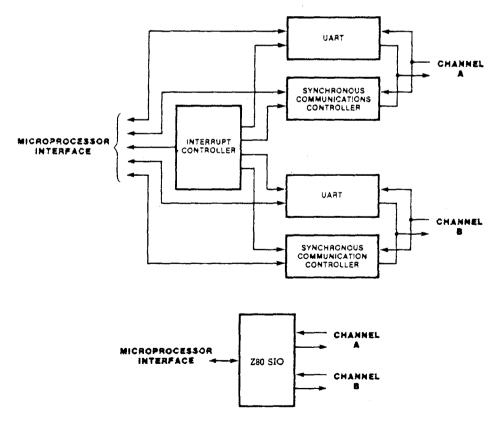

# 4.6 Z-80 S10 (Seri Giriş-Çıkış Unitesi)

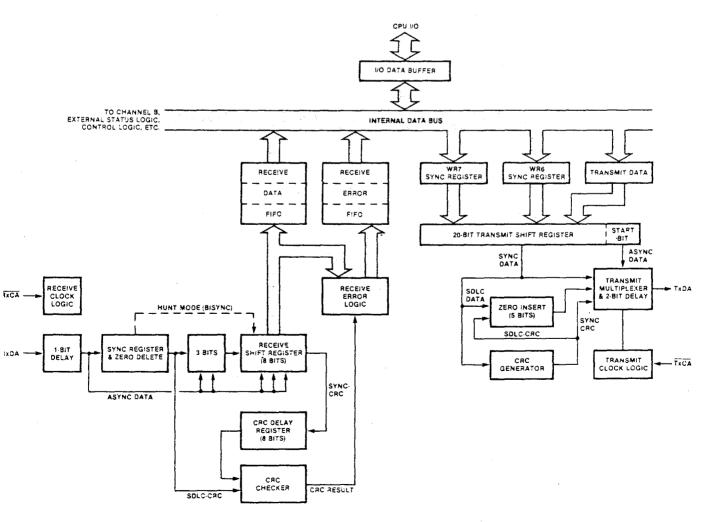

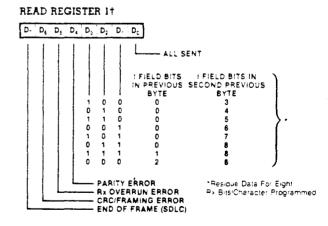

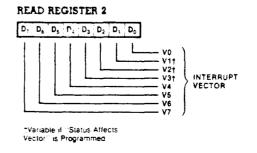

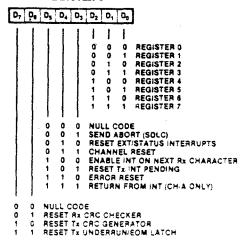

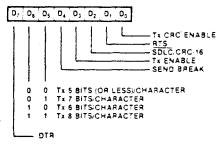

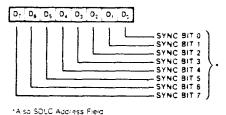

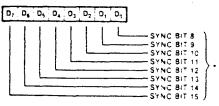

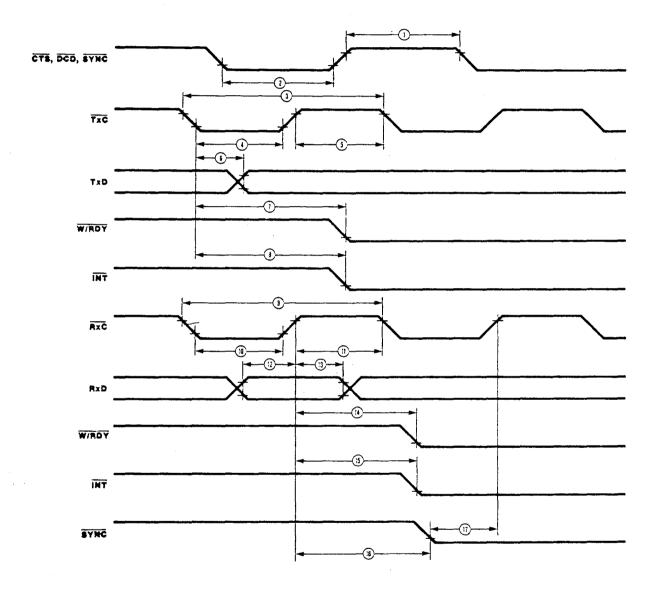

Seri haberleşme. 2-80 SIO ile yapılmaktadır. Z-80 SIO ile hem senkron hem de asenkron haberleşme yapmak mümkündür. Değişik status registerler ile SIO' nun önemli flaglerini ve hata durumlarını gözlemek mümkündür. Bu SIO devresinin mikroişlemci ile bağlantısı Şekil 4.7.a da gösterilmiştir.

Oluşturulan sistemin CPU' dan sonra en önemli Unitesidir. Bilgisayarlar arasındaki iletim SIO aracılığı ile sağlanmıştır. Bilgi iletiminde mesafenin biraz fazla olması nedeniyle SIO çıkışları TSC232 entegresi ile yükseltilmekte ve daha az kayıpla diğer SlO'ya iletilebilmektedir. TSC232 ile SIO arasındaki bağlantı sekil 4.7.b de gösterilmiştir.

(a) (b)

Şekil 4.7. Z - 80 SIO ve TSC232 Bağlantısı

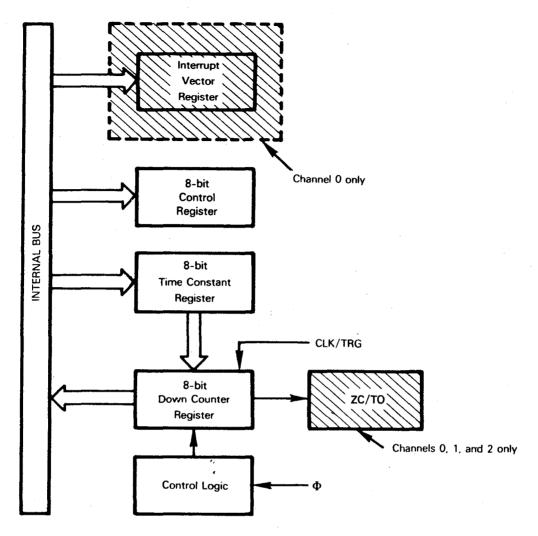

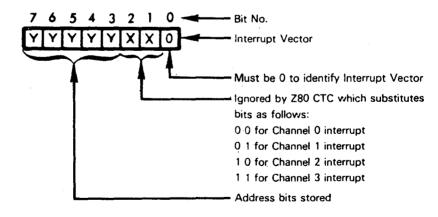

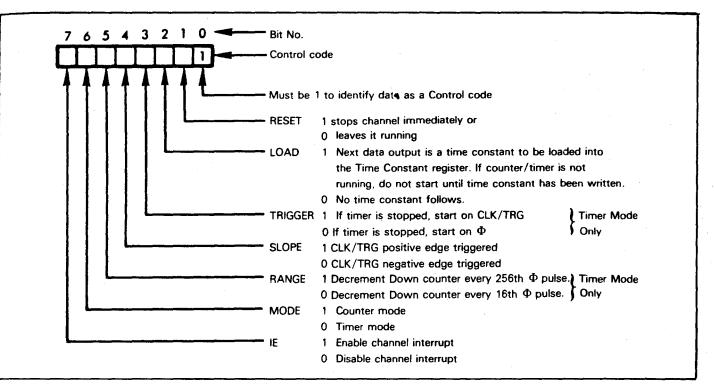

#### 4.7 Z-80 CTC (Sayıcı, Zamanlayıcı Ünitesi)

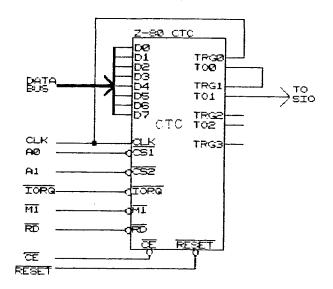

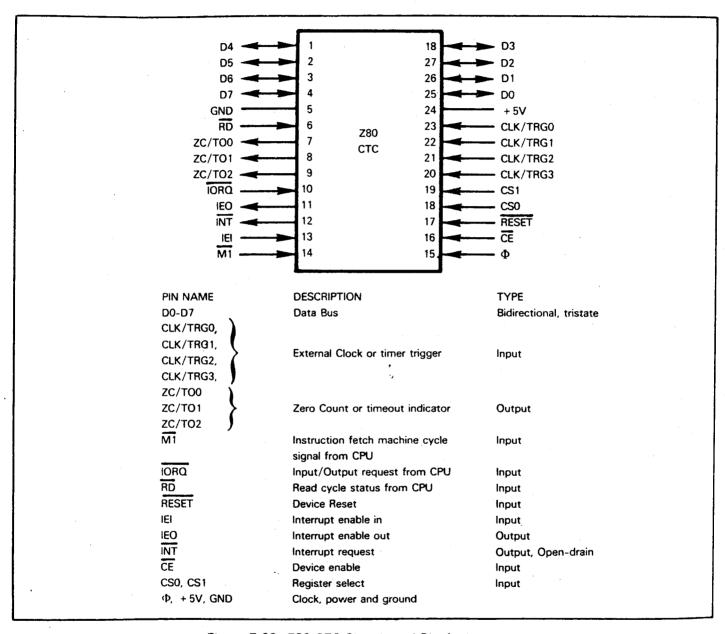

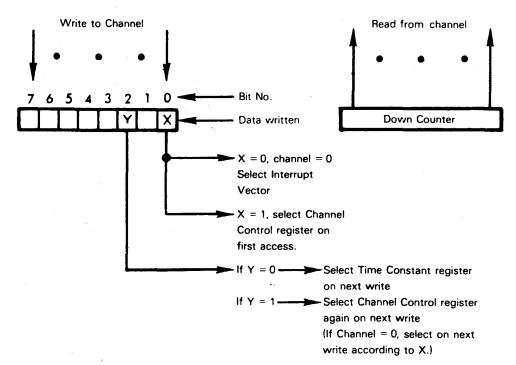

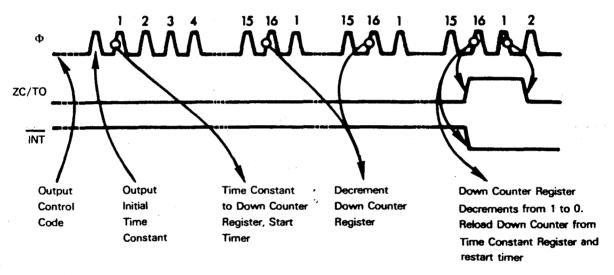

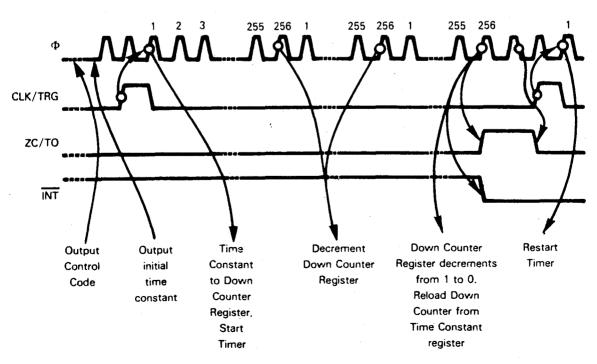

Dört kanallı sayıcı, zamanlayıcı devresi bir çok uygulamada ve tasarımda rahatlıkla kullanılmaktadır. Z-80 CTC, Z-80 CPU' ya ve Z-80 SIO' ya hiç bir ara devre gerektirmeden bağlanabilmektedir. Z-80 CTC' nin sistem içerisindeki bağlantısı şekil 4.8 de gösterilmiştir.

Şekil 4.8. Z - 80 CTC Bağlantısı

#### 4.8 Gösterge

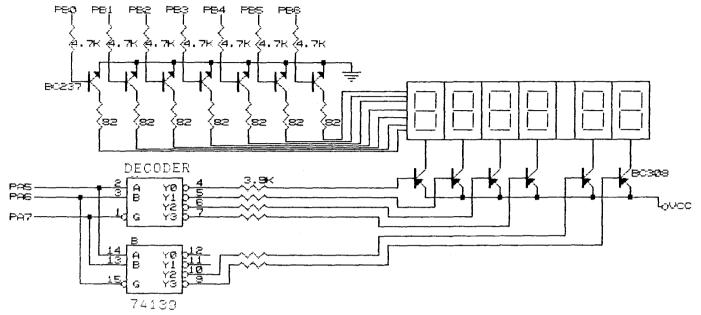

Gösterge altı adet ortak anodlu yedi parçalı displeylerden oluşmuştur. Displeylerin veri girişleri kendi aralarında paralel bağlanmıştır. Adres çözücü devre ile anod girişlerine transistörlerle besleme verilebilmektedir. Altı taneşinden yalnızca bir tanesi yanabilir. Çok hızlı bir tarama ile altı tanesininde yandığı görülebilir. Displeylerin bağlantısı şekil 4.9 da gösterilmiştir. Gösterge iki kısımdan oluşmuştur. Ilk dört displey mikroişlemcinin adres hattı bilgisini, son iki displey ise data hattı bilgisini göstermektedir.

Adres kisminda 8011, data kisminda ise 3E yaziliysa bunun anlami 8011H adresinde 3EH bulunmaktadir.

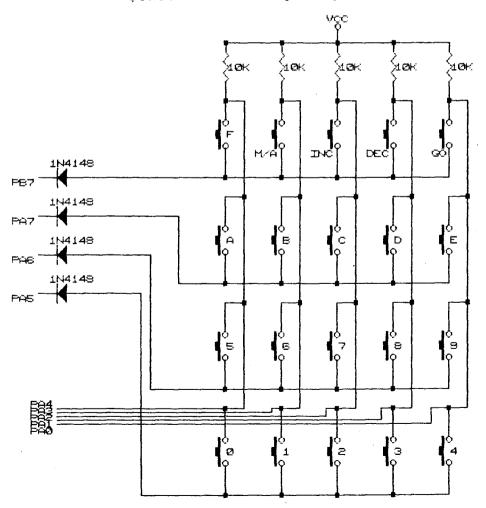

#### 4.9 Tuş Takımı

On altı adet sayı tuşu ve dört adet fonksiyon tuşundan oluşan tuş takımı devresi şekil 4.10 da görüldüğü gibi beş satır ve dört sütundan oluşan bir matris formunda tasarlanmıştır. Devreye ilave edilen bu gösterge ve tuş takımı ile PC bilgisayardan bağımsız olarak merkez mikroişlemcisine program yazılıp bağlı ünitelere bilgi gönderilebilir.

Şekil 4.9 Gösterge Bağlantısı

Şekil 4.10. Tuş Takımı

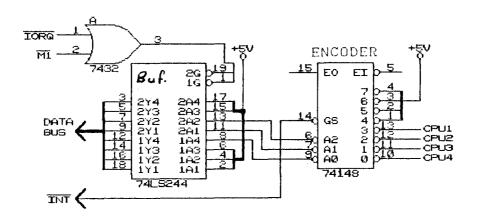

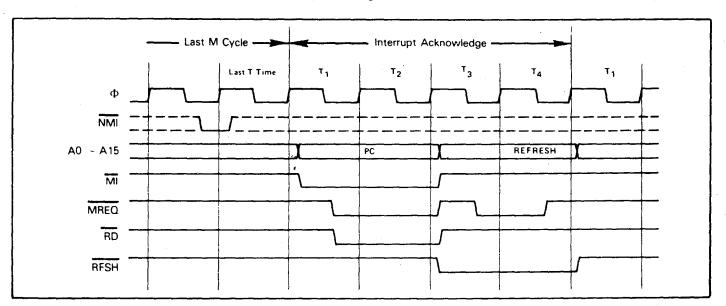

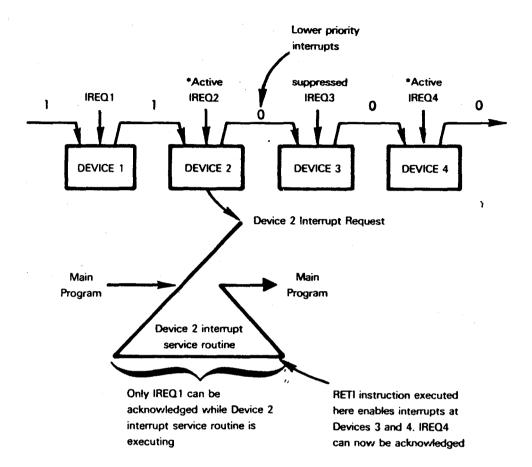

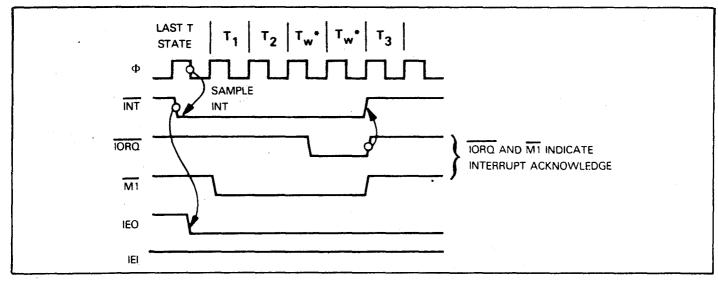

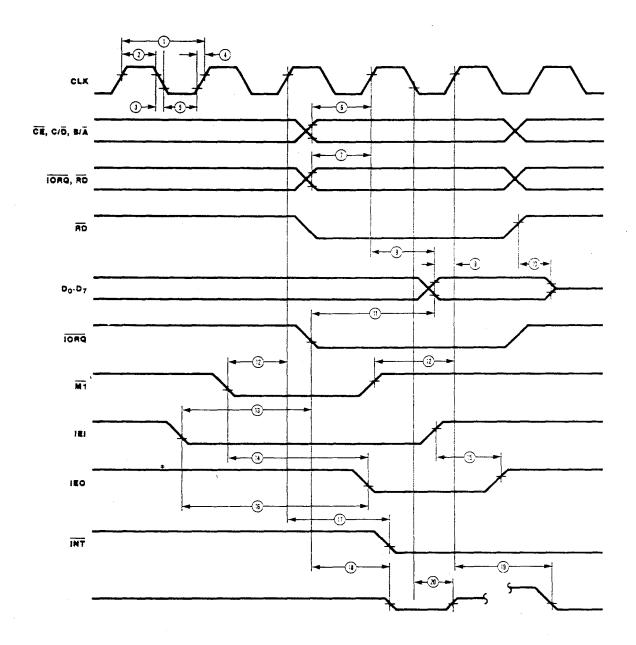

### 4.10 Interrupt Ara Devresi

Merkez bilgisayar ile yardımcı bilgisayarlar arasındaki haberleşmeyi uyum içinde yapabilmek için bir ara devre tasarlanmıştır. Bu ara devre ile yardımcı üniteler arasında bir öncelik sırası oluşturulmuştur. Aynı zamanda bu devre Z-80 CPU'nun interrupt mode O durumu için kullanılan ara devredir. Bu devrenin sisteme bağlanışı şekil 4.11 de gösterilmiştir.

Şekil 4.11. Interrupt ara Devresi

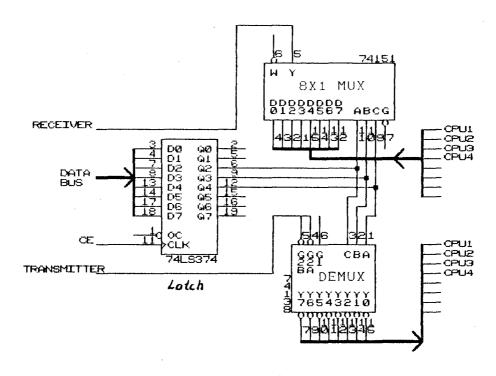

Şekil 4.12 Mux - Demux Bağlantısı

Şekil 4.12 de ise merkez ünite ile yardımcı üniteler arasında seri data transferi için bağlantıyı kurmakta kullanılan MUX ve DEMUX bağlantıları gösterilmiştir. Bu MUX ve DEMUX'ın seçici sinyalleri uygun konumlara ayarlanarak istenen ünite ile haberleşme yapılabilir.

# 4.11 Sistemin Çalışması

Her ünite açılışta ROM'da bulunan programı çalıştırır ve bu programa göre kavşaklardaki trafik ışıkları kontrol edilir. Bu Sistem genel olarak üç yardımcı ünite. merkezi unite ve bu merkezi üniteye bağlı bir PC bilgisayardan oluşmuştur. PC bilgisayarında yazılan programda saat sürekli olarak kontrol edilir ve saate uygulanacak program numarasi belirlenir. Belirlenen programla ilgili bilgiler seri porttan merkezi uniteye gönderilir. Merkezi ünitede kullanılan 'interrupt' ara devresi ile bilginin hangi uniteden geldiği belirlenir ilgili alt programa atlanır. Alt programda ilk olarak yapılan belirlenen ünite ile merkezi ünite arasındaki bilgi hattını kontrol eden MUX - DEMUX yapısında uygun 'select'ler gönderilir ve merkezi unite ile bilgi gönderen arasındaki bilgi hattı birleştirilir. Birleştirilen bilgi hattından gelen veri alınır ve hafızaya yazılır. Merkezi Uniteye PC den gelen bilgi sıra ile diğer yardımcı unitelere gonderilir. Bu işlem yapılırken her unite ile merkezi Unite arasındaki bilgi hattı MUX - DEMUX 'ın 'select'leri aracılığı ile uygun konuma getirilir ve transfer işlemi yapılır. Yardımcı Unitelerde çalıştırılan numaraları uniteler tarafından her programların faz başlarında merkezi üniteye bildirilir. Merkezi üniteye gönderilen program numaraları merkezi ünitede kontrol edilir ve farklılık varsa çalışması gereken program verileri ilgili Hemen sonra da merkezi uniteye gönderilir. program numaraları bilgisayara gönderilir ve calismasi gereken program olup olmadığı kontrol edilir. Kontrol sonucunda, program numaraları aynı ise tüm üniteler normal çalışmasına devam edecektir, farklı ise işlenmesi gereken program verileri bilgisayardan merkezi üniteye gönderilir. Merkezi üniteye gelen veriler diğer ünitelere sıra ile gönderilir ve kontrollü ve uygun şekilde tüm ünitelerin çalışması sağlanır (9,10,11,12).

Merkezi üniteden üç üniteye veri gönderme işlemi 'interrupt' ve MUX-DEMUX ara devreleri kullanılarak yapılmaktadır. Bunların yanında sistemde koordine çalışan iki ünite bulunmaktadır. Bu iki ünite ardı ardına gelen iki tane dört yollu kavşağı kontrol etmektedirler. Bu iki ünite ile merkezi ünite arasında bir çevre (loop connection) bağlantısı yapılmıştır. Bu şekilde yapılarak ard arda gelen iki kavşağın koordine çalışması sağlanmış, taşıtların ve yayaların kavşaklardaki beklemeleri önlenmiştir (11,13).

Bütün bunların yanında bağımsız çalışan ünitelerden birisine diğerlerinden farklı olarak bir yaya ışığı kontrol ilave edilmiştir. Bu tuşun görevi, taşıtlara yeşil ışık yanarken yayaları öncelikli duruma getirmektir. Tusa basıldığında uniteyi yönlendiren (kontrol eden mikroislemciye bir NMI (Non Maskable Interrupt) 'interrupt' gitmekte ve bu 'interrupt' isteğinden bir müddet sonra tüm yönden gelen araçlara 3 sn süre ile sarı ışık yanmaktadır. Sarı ışıktan sonra taşıtlara kırmızı, yayalara ise yeşil ışık yanmaktadır. Yayalara belirli bir süre yeşil yandıktan sonra kırmızıya dönüşmektedir. Uç saniye koruma süresinden sonra en son geçiş hakkına səhip olan yöne sar ışık yanmakta ve sonra yeşile dönmektedir. Bundan sonra normal akış devam etmektedir. Kavşaklarda uygulanacak devre kavşaktaki trafik yoğunluğuna göre değiştirilmektedir. şekilde düzenli ve geçikmelerin çok az olduğu bir akışı sağlanmaktadır. Bu devre süreleri gözlemle yapılan istatistikler sonucunda alınan veriler dikkate alınarak ampirik denklemlerle bilgisayarla hesaplanır (14,15).

#### 5. YAZILIM

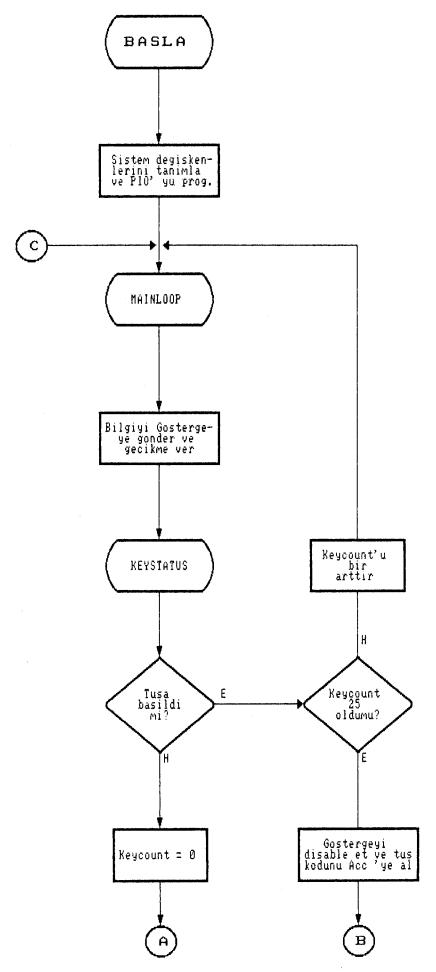

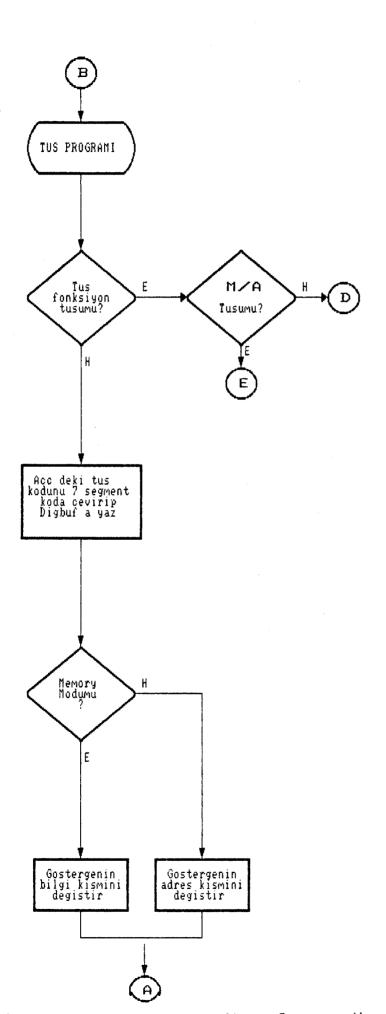

Sistem programları alt programlar halinde yazılmış olup istenen bir programdan diğer bir programa geçmek mumkundur. Alt programlara ulaşmada daha çok interrupt fonksiyonları kullanılmıştır. Butun sistem PC Bilgisayarında yazılan program ile idare edilir. Yerine getirilecek fonksiyona göre ilgili alt program çalıştırılır ve fonksiyonun gerçekleştirilmesi sağlanır. Her işlemden sonra sistem programına dönülür.

### 5.1 Akış Şemaları

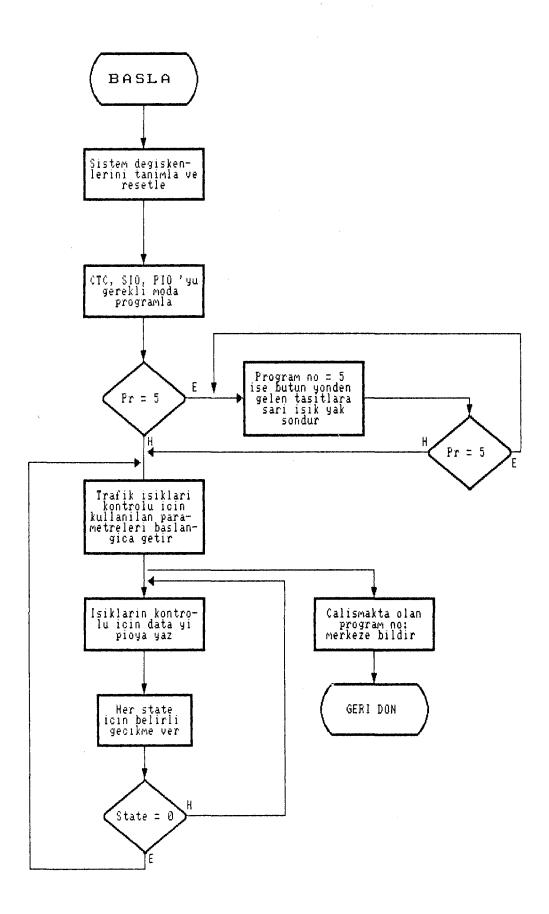

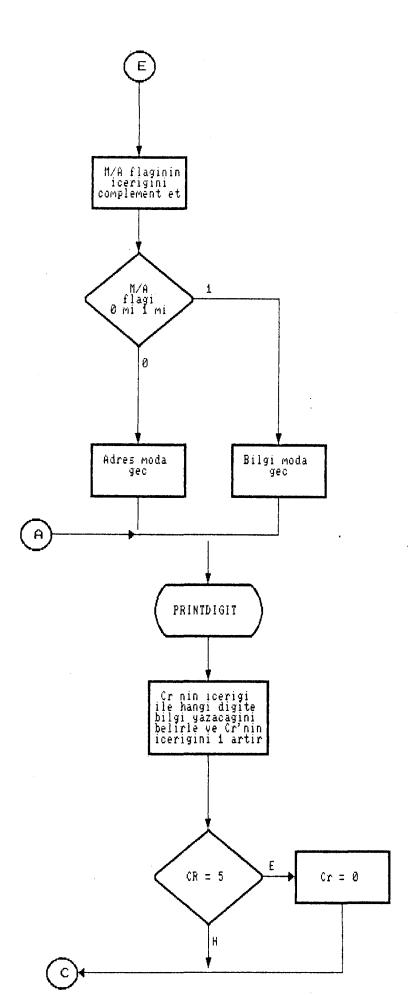

Sisteme enerji verildiğinde her kavşaktaki mikroişlemci merkezden bağımsız olarak ROM' unda bulunan programı çalıştırır ve bu şekilde kavşaktaki ışıkların merkezden bilgi gelinceye kadar kontrolu sağlanmış olur (Şekil 5.1).

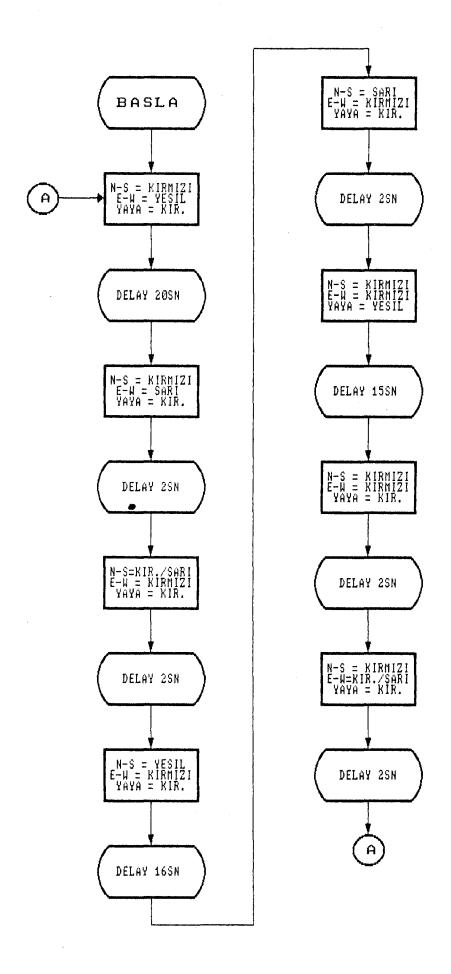

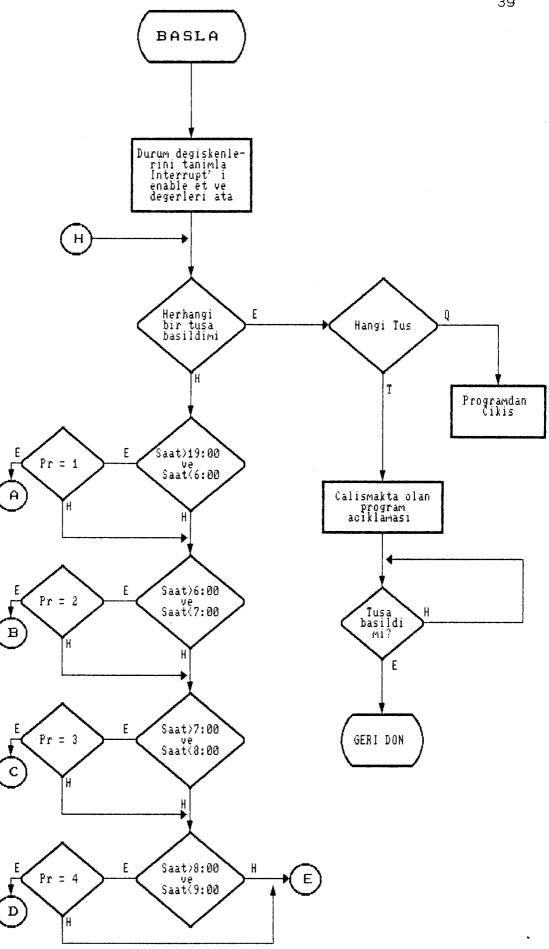

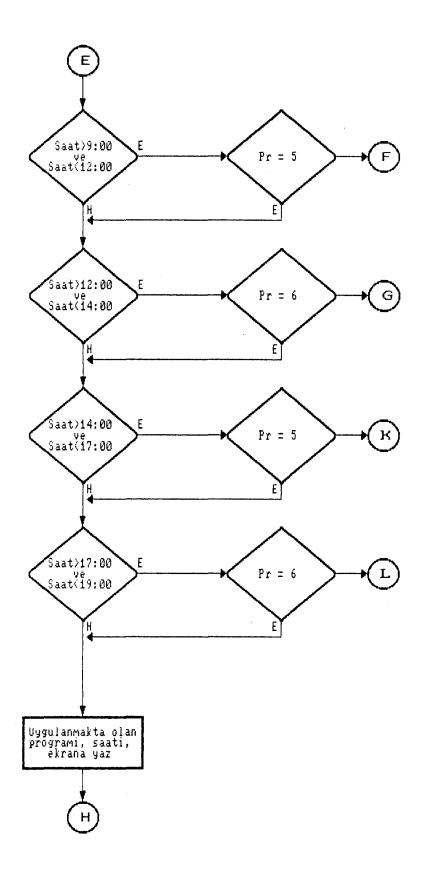

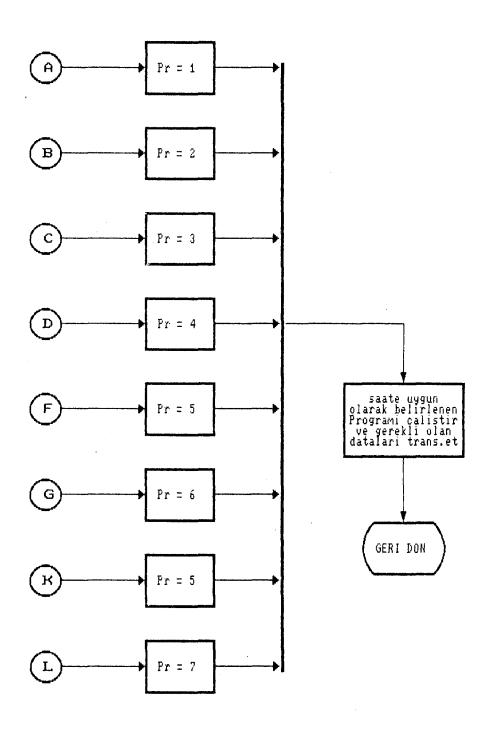

Bir kavşakta uygulanan akış diyagramı şekil 5.2 de gösterilmiştir. PC Bilgisayarındaki sistem çalışmaya başladığı andan itibaren sistem trafik yoğunluğuna qore duzenli bir şekilde çalışmaya başlar. Bu da programında saatin kontrol edilmesi ve belirlenen saatlere göre uygun programların çalıştırılması ile gerçekleştirilir. Günün değişik saatlerinde trafik yoğunluğu farklı olduğundan kavşaklarda uygulanan devre sürelerinin trafik yoğunluğuna göre düzenlenmesi gerekir. Bunun için belirlenen saatlerde gereken devre sureleri bilgisayardan uygulanması mikroişlemciye, oradan da kavşaklardaki mikroişlemcilere gönderilir. Bu şekilde de kavşaklardaki trafik akışı trafik yoğunluğuna 💎 göre değiştirilir. Akşam, belli bir saatten sonra ve sabah belli bir saate kadar olan surede yanıp sönmesi sağlanır. Başlangıçta saat kontrol edilir ve bunun sonucunda saat 6:00 dan küçükse veya 19:00 buyükse bir numaralı program, 6:00 -7:00 saatleri iki numaralı program, 7:00 arasında ise 8:00 saatleri üç numaralı program, 8:00 -9:00 saatleri arasında ise ise dört numaralı program, 9:00 - 12:00 saatleri arasında ise beş numaralı program, 12:00 -14:00 saatleri. arasında

arasında ise altı numaralı program, 14:00 - 17:00 saatleri arasında ise beş numaralı program ve 17:00 - 19:00 saatleri arasında ise altı numaralı program çalıştırılacaktır. Sistem programının akış şeması Şekil 5.3 de, merkezi mikroişlemcideki yardımcı sistem programı akış şeması Şekil 5.4 da gösterilmiştir. Sistem programları Ek 5' te verilmiştir.

Şekil 5.1. Kavşaktaki İşık Kontrolü İçin Akış Şeması

Şekil 5.2. Sinyalize Bir Tesisin Çalışmasının Akış Şeması

Sekil 5.3. Sistem Program: Akış Şeması

Şekil 5.3.3(stem Programı Akış Şeması (devam)

Şekil 5.3. Sistem Programı Akış Şeması (devam)

Şekil 5.4. Merkez Mikroişlemci Sistem Programı Akış Şeması

#### 6. SONUÇLAR ve UNERILER

Bu çalışmada belirlenen bazı kavşaklardaki trafik ışıklarının bir merkezden mikroişlemciler yardımı ile kontrol edilmesi gerçekleştirilmiştir. Merkezi üniteden kavşaklardaki ünitelere bilgi iletimi seri hattan (seri data transferi metodu ile) yapılmaktadır. Hazırlanan yazılım ile de günün değişen trafik yoğunluğuna göre devre süreleri belirlenmiş ve buna göre ışıkların kontrolu yapılmıştır.

Trafik ışıklarının bir merkezden ve mikroişlemcilerle kontrolü ile kavsaklarda bekleme süreleri minimuma kuyrukların indirilecek, uzun oluşmasına izin verilmeyecektir. En önemlisi de kazaların ve beklemelerde harcanan yakıtın asgari bir duzeye sağlanacaktır.

Böyle bir çalışma daha ileri bir düzeye getirilip bütün bir şehrin trafik ışıkları kontrolu yapılabilir. arasındaki gerceklestirebilmek icin de Uniteler veri transferi döşenen özel hatlar ile sağlanabilir. Bu hatlarda kullanılacak kaplolar düşük empedanslı ve gürültüsüz seçilmelidir. Cunku bu hatlarda ki gerilim düşümü kaplolarla minimum seviyeye düşürülebilir. Çok gelişmiş bir istersek, kavsaklara trafik ısık sistem kurmak kontrol eden mikroişlemci tarafından kontrol edilebilen taşıt sayıcı sensörler yerleştirilmelidir. Bu sensörler ile kavşaklardan geçen araç sayısı hakkında sürekli istatiksel Bu bilgiler doğrultusunda sistem bilgi alınır. kendi parametrelerini hesaplayabilir. Parametreler tarafından bölüm 2' de verilen ampirik denklemlere uygulanır ve bunun sonucunda trafik akışına göre sürekli değişen. Adapdif kontrol sistemi kurulmuş olur.

#### KAYNAKLAR DIZINI

- 1. Kutlu, K., 1964, Trafik etüdleri, Matbaa teknisyenleri basımevi, 138s.

- Kutlu, K., 1967, Trafik tekniği, Teknik üniversite matbaası, 372s.

- 3. Ayfer, M.Ö., 1977. Trafik sinyalizasyonu, Karayolları genel müdürlüğü matbaası, 184s.

- 4. Hobbs, F.D., 1979, Traffic planning and engineering, Pergamon press, 544p.

- 5. Tanenbaum, A.S., 1981, Computer Networks, Prentice-Hall, Inc., 518p.

- 6. Gupta, A., 1987, Multi-Microprocessors, IEEE press, 268p,

- 7. Laver, M., 1975, Computers, Communications and Society, Oxford University press, 100p.

- 8. Uffenbeck, J., 1985, Microcomputers and microprocessors the 8080, 8085 and Z-80, Prentice-Hall, Inc., 670p

- 9. Zaks, R., 1982, Programming the Z-80, Sybex, Inc., 626p.

- Greenfield, J.D., 1985, Microprocessor Handbook, John Wiley & Sons, Inc., 636p.

- 11. Ward, D.E., 1990, The American double ring system applied in London, London, viii+218p.

- 12. Antonini, C., 1981. Microcomputer programmed traffic light controls, Italy, 143 62 p.

- 13. Strawinski, T., 1983, Microcomputers in road traffic systems, Budapest, 126 137 p.

- 14. Pursula, M., 1989, Microprocessor and PC-based vehicle classification equipments using induction loops, UK, vii+199p.

- 15. Hawke, M.J., 1984, Application of microprocessor traffic controllers adding pedestrian signals to existing signalled junctions, London, 60p.

# **EKLER**

# Chapter 7 ZILOG Z80

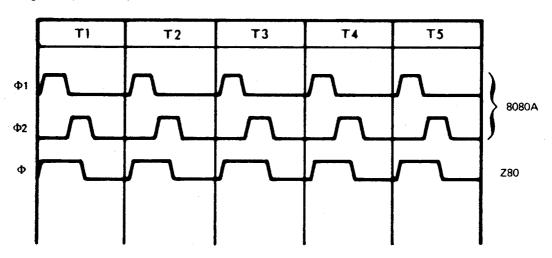

g Z80 microcomputer devices have been designed as 8080A enhancements. In fact, the same individuals consible for designing the 8080A CPU at Intel designed the Z80 devices at Zilog. The 8085, described in pter 5, is Intel's 8080A enhancement.

Z80 instruction set includes all 8080A instructions as a subset. In deference to rational necessity, rever, neither the Z80 CPU, nor any of its support devices attempt to maintain pin-for-pin compatibility with 0A counterparts. Compatibility is limited to instruction sets and general functional capabilities. A program has been written to drive an 8080A microcomputer system will also drive the Z80 system — within cerlimits; for example, a ROM device that has been created to implement object programs for an 8080A rocomputer system can be physically removed and used in a Z80 system.

Z80-8080A compatibility does extend somewhat further, since most support devices that have been gned for the 8080A CPU will also work with a Z80 CPU; therefore in many cases you will be able to upgrade 080A microcomputer system to a Z80, confining hardware modifications to the CPU and its immediate inace only.

interesting to note that the Z80 pins and signal interface is far closer than the 8085 to the three-chip 8080A figuration illustrated in 8080A chapter. Also, whereas the Z80 instruction set is greatly expanded as compared to 8080A, the 8085 instruction set contains just two new instructions. However, both the Z80 and the 8085 have lived the two most distressing problems associated with the 8080A — the three-chip 8080A CPU has in both cases a reduced to one chip, and the three 8080A power supplies have in both cases been reduced to a single +5V power solv.

G. INC., manufacturers of the Z80, are located at:

10460 Bubb Road Cupertino, California 95014

official second source for Zilog products is:

MOSTEK, INC. 1215 West Crosby Road Carrollton, Texas 75006

nannel MOS technology is used for all Z80 devices.

Z80 LSI TECHNOLOGY

# THE Z80 CPU

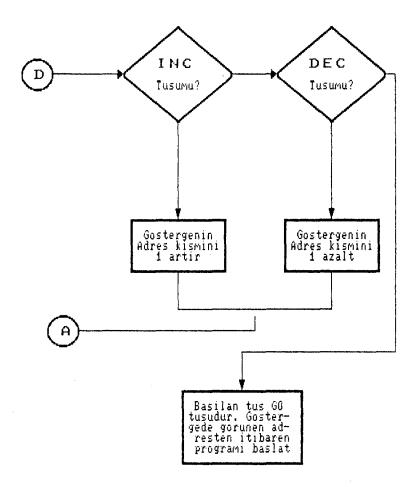

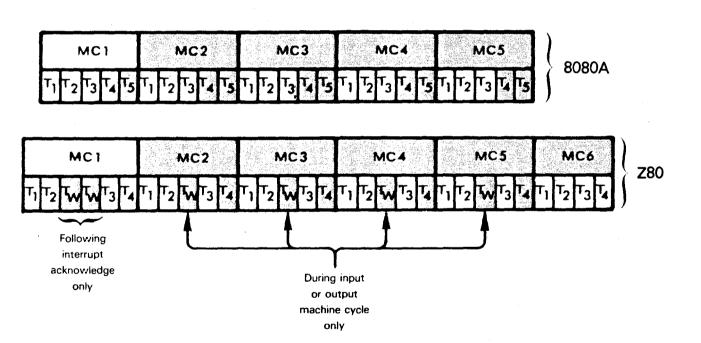

tions implemented on the Z80 CPU are illustrated in Figure 7-1. They represent "typical" CPU logic, valent to the three devices: 8080A CPU, 8224 Clock and 8228 System Controller.

# **UMMARY OF Z80/8080A DIFFERENCES**

are going to summarize Z80/8080A differences before describing differences in detail. If you know the DA well, read on; if you do not, come back to this summary after reading the rest of the Z80 CPU description. We will also contrast the Z80 and the 8085, where relevant.

he programmer, the Z80 provides more registers and addressing modes than the 8080A, plus a much larger uction set.

ificant hardware features are a single power supply (+5V), a single system clock signal, an additional interand logic to refresh dynamic memories.

Figure 7-1. Logic Functions of the Z80 CPU

e 8085 also has a single power supply and a single system clock signal. The 8085 has three additional interrupts, but ks logic to refresh dynamic memories.

# the Z80 CPU indeed the logical next 8080A evolution?

rdware aspects of the 8080A represent its weakest features, as compared to principal current competitors. ecifically, the fact that the 8080A is really a three-chip CPU is its biggest single problem; three chips are always ng to cost more than one. Next, the fact that the 8080A requires three power supplies (+5V, -5V and +12V) is a very gative feature for many users and the desirability of going to a single power supply is self-evident; the Z80 requires a gle +5V power supply. This is also true of the 8085.

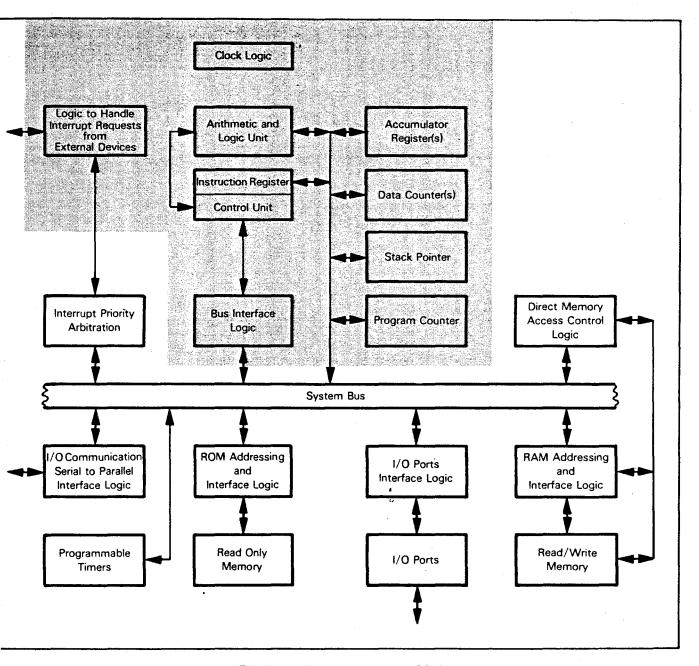

problems associated with condensing logic from three chips onto one chip are not so straightforward. Figure 7-2 iltrates the standard three-chip 8080A CPU. Let us assume that the three devices are to be condensed into a single p. Asterisks (\*) have been placed by the signals which must be maintained if the single chip is to be hardware comible with the three chips it replaces. Forty-three signals are asterisked, therefore the standard 40-pin DIP cannot be id. The problem is compounded by the fact that not all 8080A systems use an 8228 System Controller. Some 8080A tems use an 8212 bidirectional I/O port to create control signals. A few of the earliest 8080 systems use neither the 28 System Controller, nor an 8212 I/O port; rather external logic decodes the Data Bus when SYNC is true in order to nerate control signals; for example, that is how the TMS5501 works. We must therefore conclude that any attempt

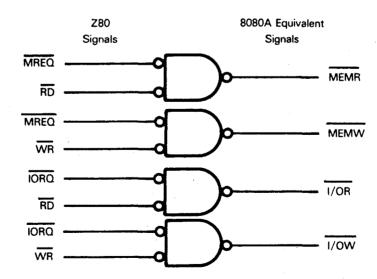

to reduce three chips to one will create a product that is not pin compatible with the 8080A; and, indeed, the Z80 is not pin compatible. What Zilog has done is include as many hardware enhancements as possible within the confines of a 40-pin DIP that must be philosophically similar to the 8080A, without attempting any form of pin compatibility. Figure 7-2 identifies the correlation between Z80 signals and 8080A signals. Notice that there is a significant similarity.

Figure 5-3 is equivalent to Figure 7-2, comparing 8085 and 8080A signals. Z80 signals are far closer to the 8080A three-chip set than the 8085.

#### Here is a summary of the hardware differences:

- The Z80 has reduced three power supplies to a single +5V power supply.

- Clock logic is entirely within the Z80.

- 3) The complex, two clock signals of the 8080A have been replaced by a single clock signal.

- 4) Automatic dynamic memory refresh logic has been included within the CPU.

- 5) Read and write control signal philosophy has changed. The 8080A uses separate memory read, memory write, I/O read and I/O write signals. The Z80 uses a general read and a general write, coupled with a memory select and an I/O select. This means that if a Z80 CPU is to replace an 8080A CPU then additional logic will be required beyond the Z80 CPU. You will either have to combine the four Z80 control signals to generate 8080A equivalents, or you will have to change the select and strobe logic for every I/O device. We will discuss this in more detail later.

- 6) Address and Data Bus float timing associated with DMA operations have changed. The 8080A floats these busses at the beginning of the third or fourth time period within the machine cycle during which a bus request occurs; this initiates a Hold state. The Z80 has a more straightforward scheme; a Bus Request input signal causes the Data and Address Busses to float at the beginning of the machine cycle; floating busses are acknowledged with a Bus Acknowledge output signal.

- 7) The Z80 has an additional interrupt request. In addition to the RESET and normal 8080A interrupt request, the Z80 has a nonmaskable interrupt which is typically used to execute a short program that prepares for power failure, once a power failure has been detected.

# Now consider internal organization of the Z80 in terms of instruction set compatibility and enhancement.

As illustrated by Table 7-3 the 8080A instruction set is, indeed, a subset of the Z80 instruction set. Unfortunately, the Z80 uses completely new source program instruction mnemonics, therefore 8080A instructions cannot immediately be identified. Technical Design Labs, Inc., has an 8080-like Z80 assembly language.

Figure 7-2. The Standard 8080A Three-Chip System and Z80 Signal Equivalents

There are very few unused object codes in the 8080A instruction set. The Z80 has therefore taken what few unused object codes there are, and used them to specify that an additional byte of object code follows:

This results in most new Z80 instructions having 16-bit object codes; but simultaneously it means that a very large number of new instructions can be added.

Any enhancement of the 8080A can include major changes within the CPU; providing the 8080A registers and status flags remain as a subset of the new design, instruction compatibility remains. These are the principal enhancements made by the Z80:

- 1) The standard general purpose registers and status flags have been duplicated. This makes it very easy to handle single-level interrupts, since general purpose register and Accumulator contents no longer need to be saved on the Stack; instead, the program may simply switch to the alternate register set.

- 2) Two Index registers have been added. This means that additional Z80 instructions can use indexed memory addressing.

- 2) An Interrupt Vector register allows external logic the option of responding to an interrupt acknowledge by issuing the equivalent of a Call instruction which vectors program execution to a memory address which is dedicated to the acknowledged external logic.

- 4) A single Block Move instruction allows the contents of any number of contiguous memory bytes to be moved from one area of memory to another, or between an area of memory and a single I/O port. You can also scan a block of memory for a defined value by executing a Block Compare instruction.

- 5) Instructions have been added to test or alter the condition of individual register and memory bits.

In contrast to the extensive enhancements of the Z80, the 8085 registers and status architecture are identical to the 8080A. There are only two additional instructions in the 8085 instruction set; however, the 8085, like the Z80, allows Call instructions to be used when acknowledging an interrupt — a particularly useful enhancement.

While on the surface the Z80 instruction set appears to be very powerful, note that instruction sets are very subjective; right and wrong, good and bad are not easily defined. Let us look at some nonobvious features of the Z80 instruction set.

First of all, the execution speed advantage that results from the new Z80 instructions is reduced by the fact that many of these instructions require two bytes of object code. Some examples of Z80 instructions and equivalent 8080A instruction sequences with equivalent cycle times are given in Table 7-1.

Table 7-1. Comparisons of Z80 and 8080A Instruction Execution Cycles

| Z80          |            |        | A0808              |                    |                            |

|--------------|------------|--------|--------------------|--------------------|----------------------------|

| Instructions |            | Cycles | Instructions       |                    | Cycles                     |

| LD           | R.(IX + d) | 19     | LXI<br>DAD<br>MOV  | H,d<br>IX<br>R,M   | 10<br>10<br><u>7</u><br>27 |

| LD           | RP,ADDR    | 20     | LHLD<br>MOV<br>MOV | ADDR<br>C.L<br>B.H | 16<br>5<br><u>5</u><br>26  |

| SET          | B,(HL)     | 15     | MOV<br>ORI<br>MOV  | A,M<br>MASK<br>M,A | 7<br>7<br><u>7</u><br>21   |

Also, a novice programmer may find the Z80 instruction set bewilderingly complex. At a time when the majority of potential microcomputer users are terrified by simple assembly language instruction sets, it is possible that users will react negatively to an instruction set whose complexity (if not power) rivals that of many large minicomputers.

Many of the new Z80 instructions use direct, indexed memory addressing to perform operations which are otherwise identical to existing 8080A instructions. Now the Z80 has two new 16-bit Index registers whose contents are added to

an 8-bit displacement provided by the instruction code; this is the scheme adopted by the Motorola MC6800. This scheme is inherently weaker than having a 16-bit, instruction-provided displacement, as implemented by the Signetics 2650. When the Index register is larger than the displacement, the Index register, in effect, becomes a base register. When the Index register has the same size, or is smaller than the displacement, it is truly an Index register as described in "Volume 1 — Basic Concepts". The Signetics 2650 implementation is more powerful.

#### **280 PROGRAMMABLE REGISTERS**

We will now start looking at the Z80 CPU in detail, beginning with its programmable registers.

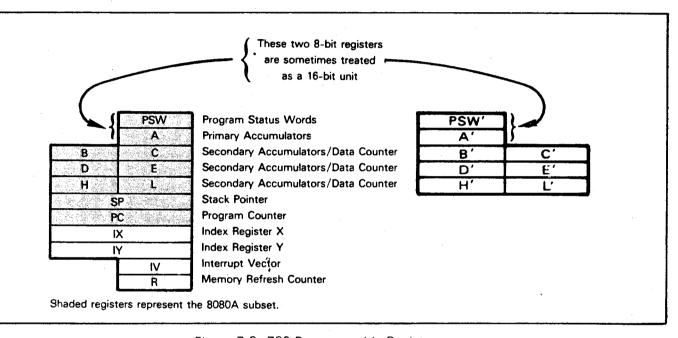

The Z80 has two sets of 8-bit programmable registers, and two Program Status Words. At any time one set of programmable registers and one Program Status Word will be active and accessible.

n addition, the Z80 has a 16-bit Program Counter, a 16-bit Stack Pointer, two 16-bit Index registers, an 8-bit nterrupt Vector and an 8-bit Memory Refresh register.

Figure 7-3 illustrates the Z80 registers. Within this figure, the 8080A registers' subset is shaded.

Figure 7-3. Z80 Programmable Registers

he Z80 uses its Program Status Word, its A, B, C, D, E, H, and L registers, plus the Stack Pointer and the Proram Counter exactly as the 8080A uses these locations; therefore no additional discussion of these registers s needed.

The Program Status Word, plus registers A, B, C, D, E, H and L are duplicated. Single Z80 instructions allow you to witch access from one register set to another, or to exchange the contents of selected registers. At any time, one or ne other set of registers, but not both, is accessible.

here are two 16-bit Index registers, marked IX and IY. These are more accurately looked upon as base registers, as vill become apparent when we examine Z80 addressing modes.

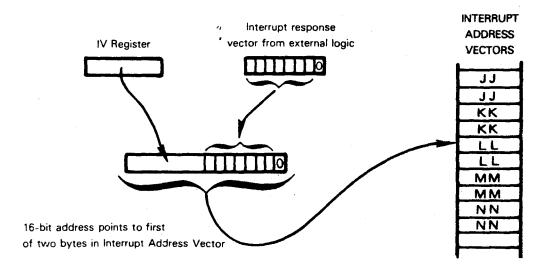

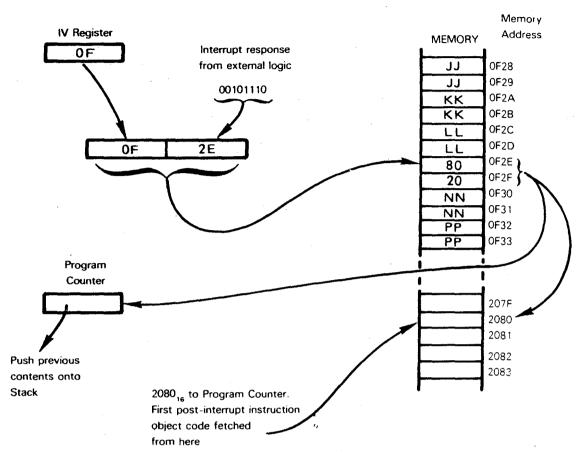

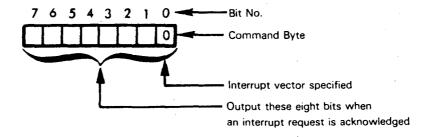

The Interrupt Vector register performs a function similar to the ICW2 byte of the 8259 PICU device (described in the 8080A chapter). Z80 interrupt acknowledge logic gives you the option of initiating an interrupt service routine with a Call instruction, where the high order address byte for the call is provided by the Interrupt Vector register. The 085 also provides this capability.

the Memory Refresh Counter register represents a feature of microcomputer systems which has been over-boked by everyone except Fairchild and Zilog. Dynamic memory devices will not hold their contents for very long, respective of whether power is off or on. A dynamic memory must therefore be accessed at millisecond intervals. Bynamic memory devices compensate for this short-coming by being very cheap — and dynamic refresh circuitry is ery simple. Using a technique akin to direct memory access, dynamic refresh circuitry will periodically access dynamic memories, rewriting the contents of individual memory words on each access. About the only logic needed by dynamic effesh is a counter via which it keeps track of its progress through the dynamic memory; that is the purpose of the Z80 Memory Refresh Counter register. The Z80 also has a special DMA refresh control signal; therefore the Z80 provides much of the dynamic refresh logic needed by dynamic memory devices.

#### **Z80 ADDRESSING MODES**

Z80 instructions use all of the 8080A addressing modes; the Z80 also has these two enhancements:

- 1) A number of memory reference instructions use the IX and IY registers for indexed, or base relative addressing.

- 2) There are some two-byte program relative Jump instructions.

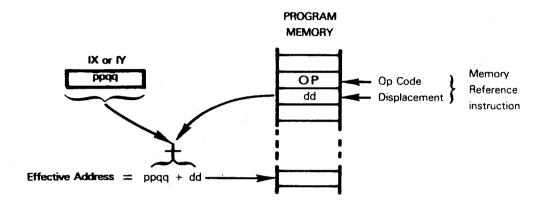

A memory reference instruction that uses the IX or IY register will include a single data displacement byte. The 8-bit value provided by the instruction object code is added to the 16-bit value provided by the identified Index register in order to compute the effective memory address:

Z80 INDEXED ADDRESSING

p, q and d represent any hexadecimal digits; dd represents an 8-bit, signed binary value.

This is standard microcomputer indexed addressing and is less powerful than having the memory reference instruction provide a 16-bit base address or displacement; for a discussion of these addressing modes see "Volume 1 — Basic Concepts", Chapter 6.

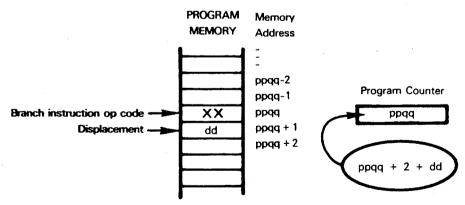

The program relative, two-byte Jump instructions provided by the Z80 provide standard two-byte, program relative addressing. A single, 8-bit displacement is provided by the Jump instruction's object code; this 8-bit displacement is added, as a signed binary value, to the contents of the Program Counter — after the Program Counter has been incremented to point to the sequential instruction:

The next instruction object code will be fetched from memory location ppqq+2+dd. p. q. and d represent any hexadecimal digits. dd represents a signed binary, 8-bit value.

For a discussion of program relative addressing, see "Volume 1 - Basic Concepts".

#### The Z80 addressing enhancements are of significant value when comparing the Z80 to the 8080A.

The value of the Index register comes not so much from having an additional addressing option, but rather IX and IY allow an efficient programmer to husband his CPU register space more effectively. Look upon IX and IY as performing memory addressing tasks which the 8080A would have to perform using the BC and DE registers. By freeing up the BC and DE registers for data manipulation, you can significantly reduce the number of memory reference instructions executed by the Z80.

The two-byte program relative Jump instruction is useful because in most programs 80% of the Jump instructions branch to a memory location that is within 128 bytes of the Jump. That is the rationale for most microcomputers offering two-byte as well as three-byte Jump instructions.

#### **Z80 STATUS**

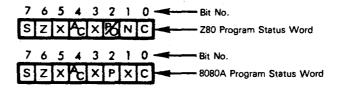

The Z80 and 8080A both use the Program Status Word in order to store status flags. These are the Z80 status flags:

Carry (C)

Zero (Z)

Sign (S)

Parity/Overflow (P/O)

Auxiliary Carry (A<sub>C</sub>)

Subtract (N)

Statuses are recorded in the Program Status Word by the Z80, as compared to the 8080A, as follows:

The Parity/Overflow and Subtract statuses differ from the 8080A. All other statuses are the same. Note that the Z80, like the 8080A, uses borrow philosophy for the Carry status when performing subtract operations. That is to say, during a subtract operation, the Carry status takes the reciprocal value of any Carry out of the high-order bit. For details see the 8080A Carry status descriptions given in the 8080A chapter.

The 8080A has a Parity status but no Overflow status. The Z80 uses a single status flag for both operations, which makes a lot of sense. The Z80 Overflow status is absolutely standard, therefore only has meaning when signed binary arithmetic is being performed — at which time the Parity status has no meaning. Within the Z80, therefore, this single status is used by arithmetic operations to record overflow and by other operations to record parity. For a complete discussion of the Overflow status see "Volume 1 — Basic Concepts"

The Subtract status is used by the DAA instruction for BCD operations, to differentiate between decimal addition or subtraction. The Subtract and Auxiliary Carry statuses cannot be used as conditions for program branching (conditional Jump, Call or Return instructions).

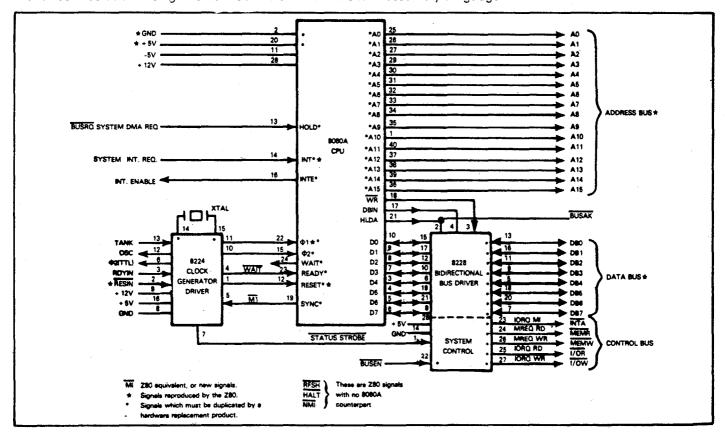

#### **Z80 CPU PINS AND SIGNALS**

The Z80 CPU pins and signals are illustrated in Figure 7-4. Figure 7-2 provides the direct comparison between Z80 CPU signals and the standard 8080A, 8228, 8224 three-chip systems.

Let us first look at the Data and Address Busses.

The 16 address lines A0 - A15 output memory and I/O device addresses. The address lines are tristate; they may be floated by the Z80 CPU, giving external logic control of the Address Bus. There is no difference between Z80 and 8080A Address Bus lines.

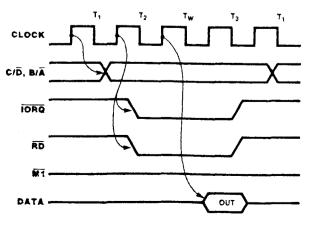

The Data Bus lines DO - D7 transmit bidirectional data into or out of the Z80 CPU. Like the Address Bus lines, the Data Bus lines are tristate. The Z80 Data Bus lines do differ from the 8080A equivalent. The 8080A Data Bus is multiplexed; status output on the Data Bus by the 8080A during the T2 clock period of very machine cycle is strobed by the SYNC pulse. The Z80 does not multiplex the Data Bus in this way. The Z80 Data Bus lines operate at normal TTL levels, whereas the 8080A Data Bus lines do not.

Control signals are described next; these may be divided into system control, CPU control and Bus control. First we will describe the System control signals.

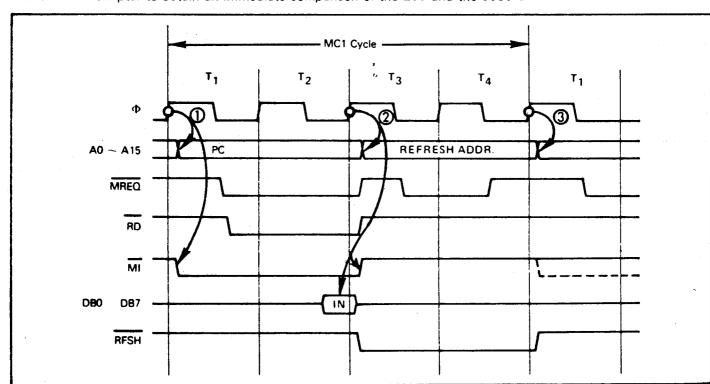

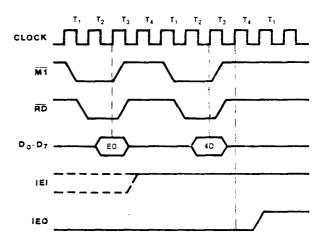

M1 identifies the instruction fetch machine cycle of an instruction's execution. Its function is similar, but not identical to the 8080A SYNC pulse. The Z80 PIO device uses the low M1 pulse as a reset signal if it occurs without IORO or RD simultaneously low.

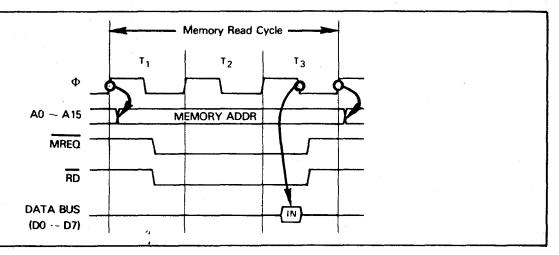

MREQ identifies any memory access operation in progress; it is a tristate control signal.

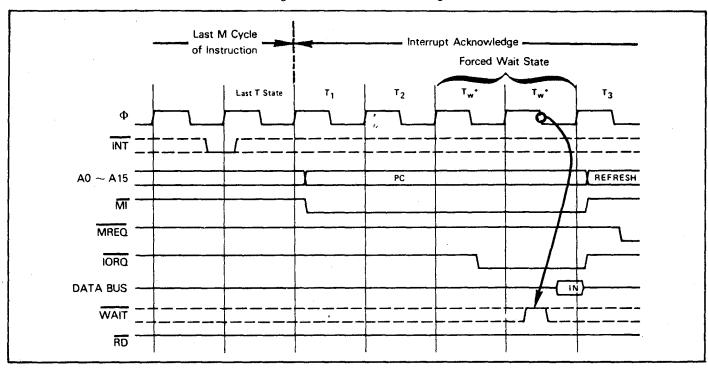

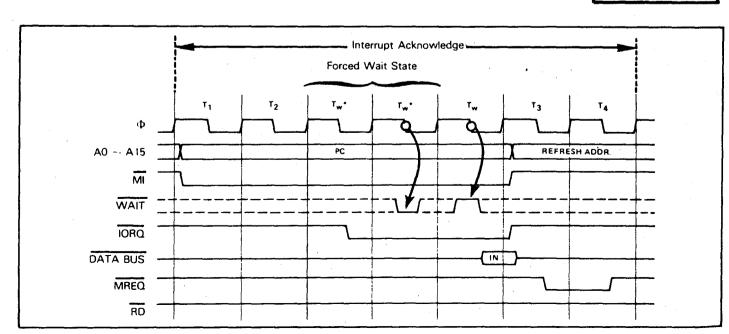

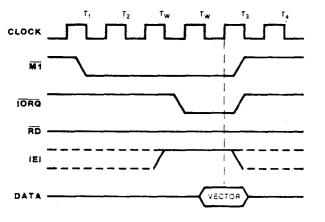

IORQ identifies any I/O operation in progress. When IORQ is low, A0 - A7 contain a valid I/O port address. IORQ is also used as an interrupt acknowledge; an interrupt is acknowledged by M1 and IORQ being output low — a unique combination, since M1 is otherwise low only during an instruction fetch, which cannot address an I/O device.

Z80 SYSTEM CONTROL SIGNALS RD is a tristate signal which indicates that the CPU wishes to read data from either memory or an I/O device, as identified MREQ or IORQ.

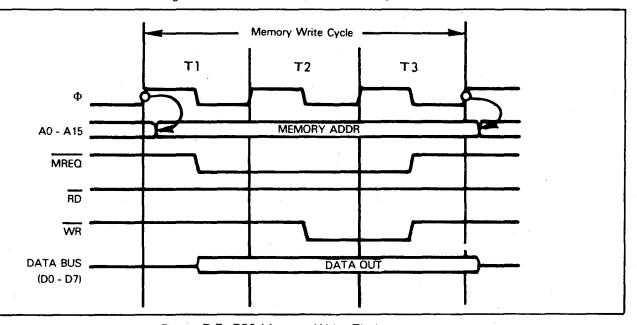

WR is a tristate control signal which indicates that the CPU wishes to write data to memory or an I/O device as indicated by MREQ and IORQ. Some Z80 I/O devices have no WR input. These devices assume a Write operation when IORQ is low and RD is high. RD low specifies a Read operation.

The various ways in which the three control signals, M1, IORQ, and RD, may be interpreted are summarized in Table 7-5, which occurs in the description of the Z80 PIO device.

RFSH is a control signal used to refresh dynamic memories. When RFSH is output low, the current MREQ signal should be used to refresh dynamic memory, as addressed by the lower seven bits of the Address Bus, A0 - A6.

Next we will describe CPU control signals.

Figure 7-4. Z80 CPU Signals and Pin Assignments

HALT is output low following execution of a Halt instruction. The CPU now enters a Halt state during which it continuously re-executes a NOP instruction in order to maintain memory refresh activity. A Halt can only be terminated with an interrupt.

Z80 CPU CONTROL SIGNALS

Z80 BUS CONTROL

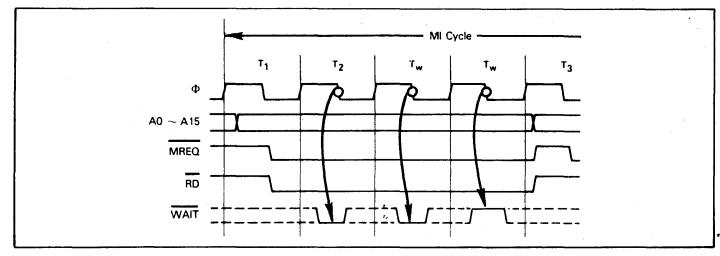

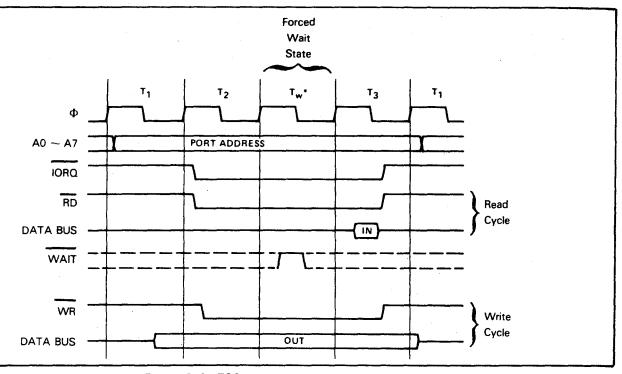

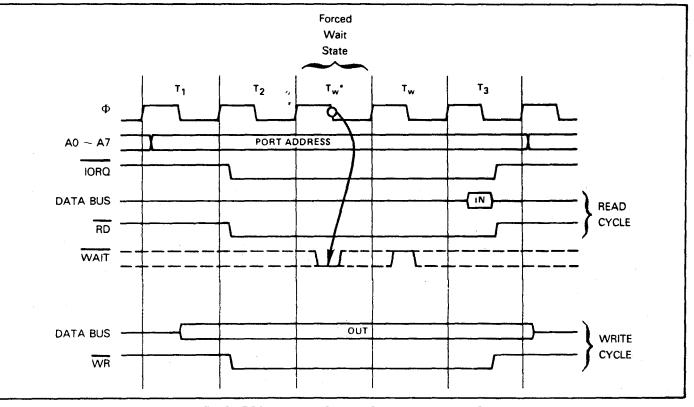

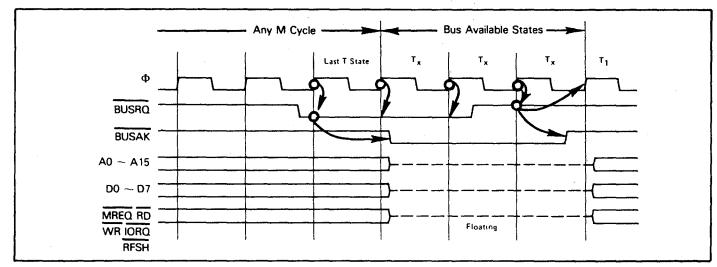

SIGNALS